Wiki

User Tools

Sidebar

Table of Contents

☚ Schaltungen ★

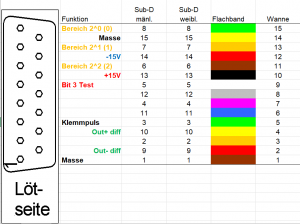

| hinten >>>>>>>>> vorne | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||

| Schaltungen: | | | | | Front | Selektor | Q+D | Signaltransfer über alles |

|

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | X | |||

| Layouts: | | | | | Front | Selected | Q+D | ||

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | MDR-IO-V2 | |||

### Bestellt und in Herstellung (Leiterkarte) ### Ersetzt!

Quick & Dirty Schaltung

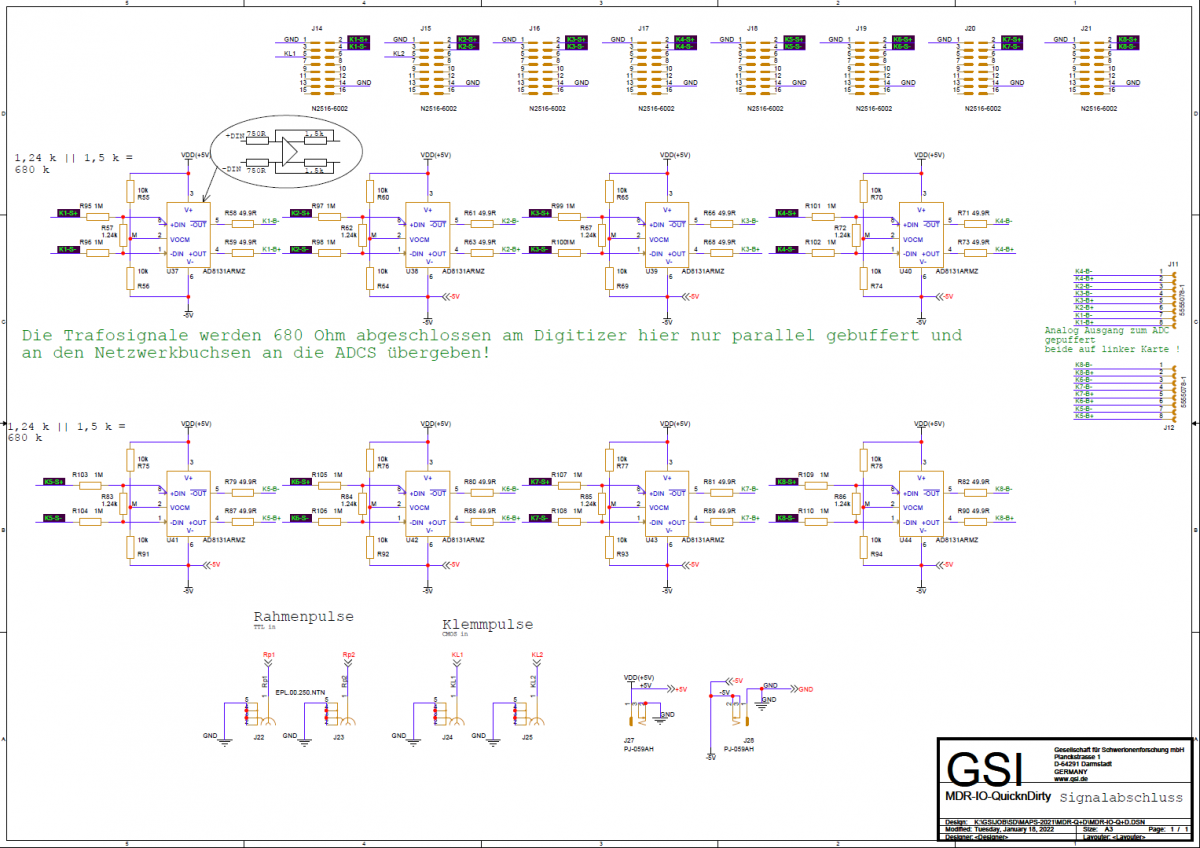

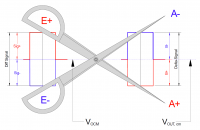

Acht Trafos (☛ Auswahl) werden hochohmig parallel abgegriffen: Es werden nur die Analogsignale abgenommen. Angesteuert wird vom alten Digitizer. Die Analogsignale werden gebuffert und differetiell 100Ω getrieben an die Adcs hinter den RJ45 Buchsen übergeben!

Projektpfad: K:\GsiJob\SD\MAPS-2021\MDR-Q+D

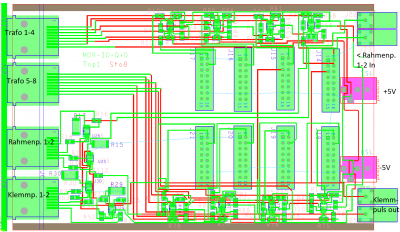

Anschluss Schema

Page 3 - Signal-Buffer

Aktuelles Problem: Eine minimal andere Version des Treibers wurde bestellt, AD8132ARMZ statt AD8131ARMZ wurde bestellt und eingesetzt. Die eingesetzte Version hat nicht die eingezeichneten internen Feedbackwiderstände. Bei der eingesetzten Version müssen die Widerstände außerhalb des Chips eingesetzt sein; das ist im Layout aber nicht vorgesehen. In Korrektur des falsch eingesetzten Treibers werden dabei zwei Varianten der Schaltung ersatzweise getestet:

1.) Rückkopplung ß2 =1, ß1 = 0 (kein Feedback), K1

2.) Externe Feedbackwiderstände RF = 2 MΩ, K2

3.) Keine Rückkopplung ß2 =0, ß1 = 0 (kein Feedback), K3-8:

| ☛ ♠ Ergebnis der durchgeführten Messungen ist mittlerweile, das eine Verstärkung 1:1 am sinnvollsten ist. Dazu betragen die vier Widerstände RG RF alle 1 MΩ, um das laufende MAPS nicht zu beeinflußen in seinem Signal. Im neuen MAPS-2021 betrügen diese Widerstände im Standalonebetrieb dann alle 340 Ω. Die Eingangsimpedanz würde dann wie gewollt 680 Ω betragen! Der an den Eingängen parallele Widerstand 1,24k verändert dagegen die Verstärkung und wird nicht eingesetzt! ☛ ♠ Weiter ist somit die Benutzung des Bausteins mit externen Feedbackwiderständen AD8132ARMZ sinnvoller als des Bausteins mit eingebauten 2:1-Verstärkungsnetzwerk “AD8131ARZ! |

| Eingang Buffer | Buffer | Ausgang |

|---|---|---|

| Sig+ an W2-rot Sig- an W4-gelb am Flachband (s.ob.) |  | Ch1-gelb = Sig+ Ch2-blau = Sig- Ossziabgriff Pol. wie Plan unten Signal am ADC wg. Dokumenten Inkonsistenz! |

Leider schwang das System: Lag an eingesetzten Billigsteckernetzteilen, getaktet. Nun durch Labornetteil ersetzt!

| Messungen: | ||

|---|---|---|

| Labor | LSB4 Anlage | Software GUI |

| ★ M1 verschiedene ext. Anpassg. | ★ M4 verschiedene ext. Anpassg. | SW1 |

| ★ M2 verschiedene ext. Anpassg. | ||

| ★ M3 verschiedene ext. Anpassg. Auch mit Einzelpulser! | ||

| ★ M5 komplementär mit Trafo | ||

| ★ M6 Alles 1 MΩ | ||

![]() Aufgrund von Diskrepanzen in den gestellten Trafounterlagen ist das Signal negiert angeschlossen: Sig+ an Pin9 und Sig- an Pin10 1) statt wie in Zusammenstellung H. Bräuning und Flachband-T-Stück oben!

Aufgrund von Diskrepanzen in den gestellten Trafounterlagen ist das Signal negiert angeschlossen: Sig+ an Pin9 und Sig- an Pin10 1) statt wie in Zusammenstellung H. Bräuning und Flachband-T-Stück oben!

![]() Am Kanal K7 wird umgekehrt polar gemessen (nur Osszy), da die orangen Adern falsch umgekehrt abgegriffen wurden: Sig+ ist NICHT dunkel blau — sondern hellblau!

Am Kanal K7 wird umgekehrt polar gemessen (nur Osszy), da die orangen Adern falsch umgekehrt abgegriffen wurden: Sig+ ist NICHT dunkel blau — sondern hellblau!

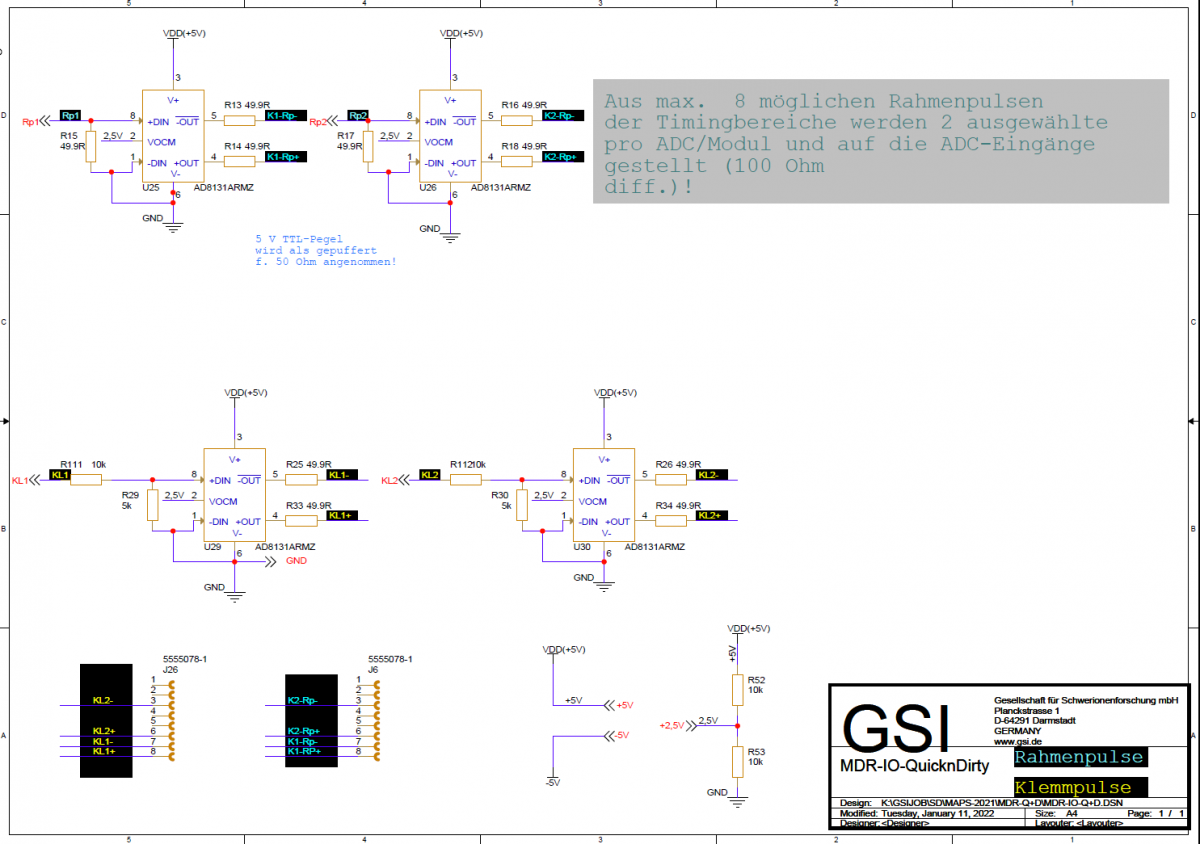

Page 2 - Rahmen+Klemm

1.) Bezüglich der Rahmenpulse wird von 50 Ω getriebenen TTL-Pegeln single ended bezogen auf Masse ausgegangen als Eingangssignal.

2.) Die Rahmenpulse haben CMOS-Pegel (12-15V) bezogen auf Masse. Sie werden parallel zwischen Treiber (Digitizer) und Trafo-Kopfelektronik abgegriffen. Der Klemmpuls ist am Trafo mit 12,7 kΩ abgeschlossen. Er wird daher herunter geteilt auf TTL-Pegel!

☚ Schaltungen ★