Wiki

User Tools

Sidebar

Table of Contents

☚ Schaltungen ★

| hinten >>>>>>>>> vorne | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||

| Schaltungen: | | | | | Front | Selektor | Q+D | Signaltransfer über alles |

|

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | X | |||

| Layouts: | | | | | Front | Selected | Q+D | ||

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | MDR-IO-V2 | |||

### Bestellt und in Herstellung (Leiterkarte) ### Ersetzt!

MDR-IO-V1

Längsboard zur Übergabe IO-Signale an IO-Karte:

Seite 1 - Pegelwandler-IO

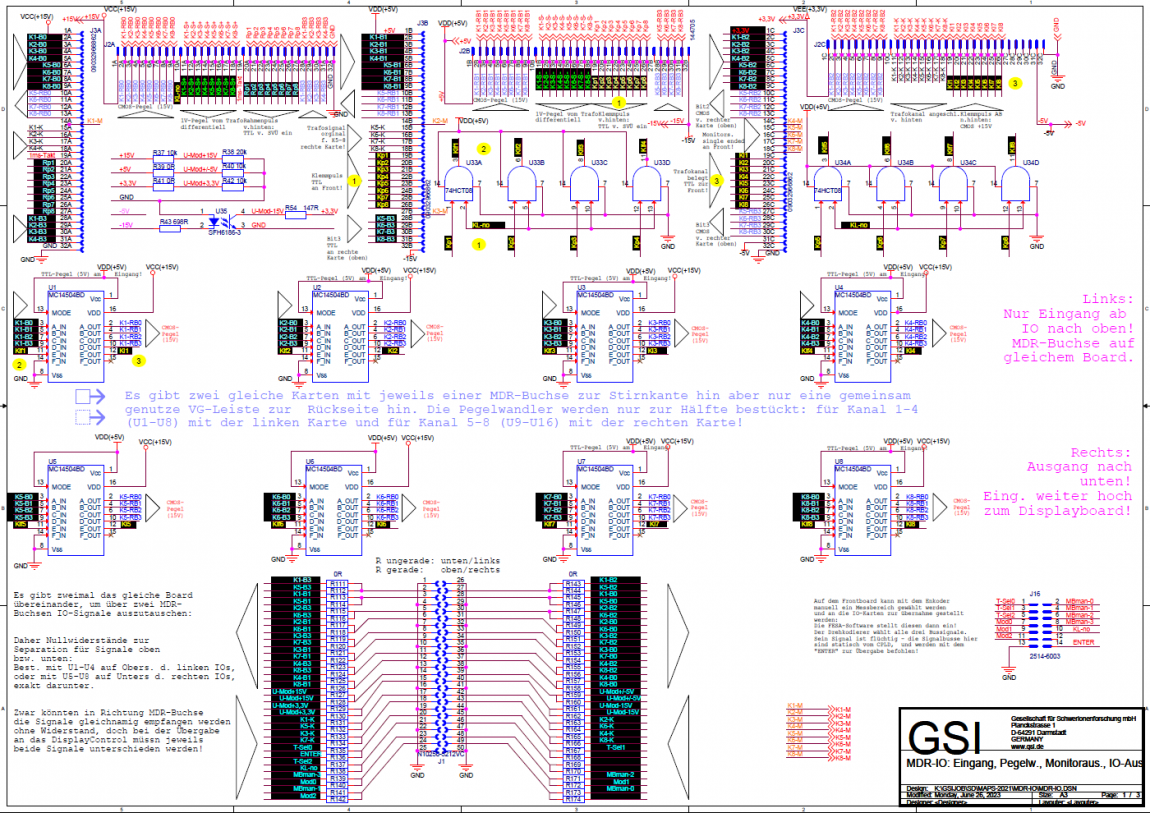

Mit hinterer VG-Leiste und seitlicher VG-Leiste zur Frontplatte. Die erste Seite enthält zweistufig Pegelumsetzer von LVTTL (IO) → TTL (Anzeige) → CMOS (15V) für die Trafos.

Pegelerörterung

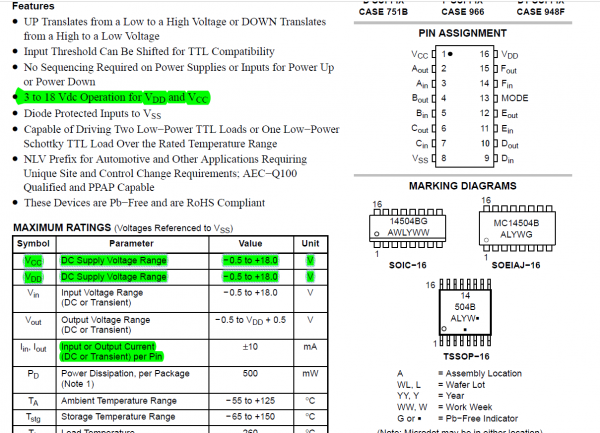

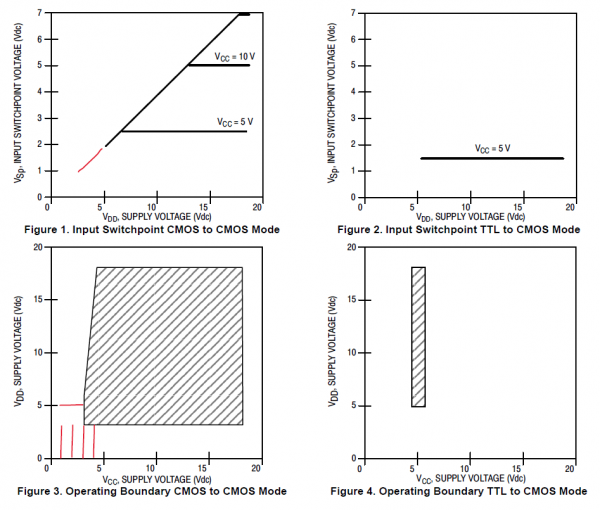

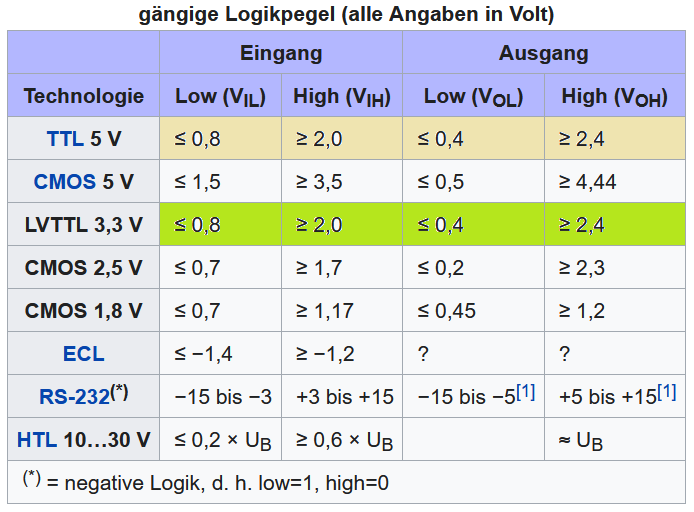

Die von den DAC-IOs gestellten Steuerpegel sind LVTTL 3,3V — die Trafos benötigen CMOS 12-15V! Die Pegelwandlung mit dem vorgesehenen Baustein erfolgt einstufig (Designänderung): Der Einsatz von TTL-Eingangspegeln am Wandler akzeptiert auch LVTTL-Pegel. Damit kann direkt zu 15V-CMOS-Pegeln übergegangen werden! Das geht, da der Eingangspegel des Wandlers gewählt werden kann: der Mode Pin auf +5V wählt eingangseitig TTL! Ausgangsseitig gibt es nur CMOS-Pegel mit wählbaren Ausgangsspannungen. Das Feld im vierten Quadranten von Diagramm fordert nur die eingangsseitige Versorgungsspannung von 5V. Der erlaubte Pegel für ein Eingangs-High ist aber der angegebene für TTL und der erlaubt 3,3V. Die Darstellung der Messbereichsbits erfolgt durch 3,3V-CPLDs gesteuert, sodaß diese direkt, wie von der DAC-IO kommend, ausgewertet werden können!

Zum Arbeiten mit 3,3V-Pegeln mit CMOS-Technik wäre ein zweistufiges Umsetzen notwendig, da wie Diagr2. an den roten Markierung zeigt, eine direkter Übergang zu 15V-CMOS nicht möglich spezifiziert ist. Die grün unterlegten Abgangspegel der DAQ mit LVTTL gewähren nominell nicht die Zwischenstufe 5V-CMOS, deswegen 5V TTL mit den beige unterlegten Pegeln oben!

VCC noch ändern auf +5V-TTL!

Schaltpläne

Geänderte Widerstandswerte:

Bei Optokoppler SFH6186-3 ist:

- R43 auf 750R

- R54 auf 150R

geändert.

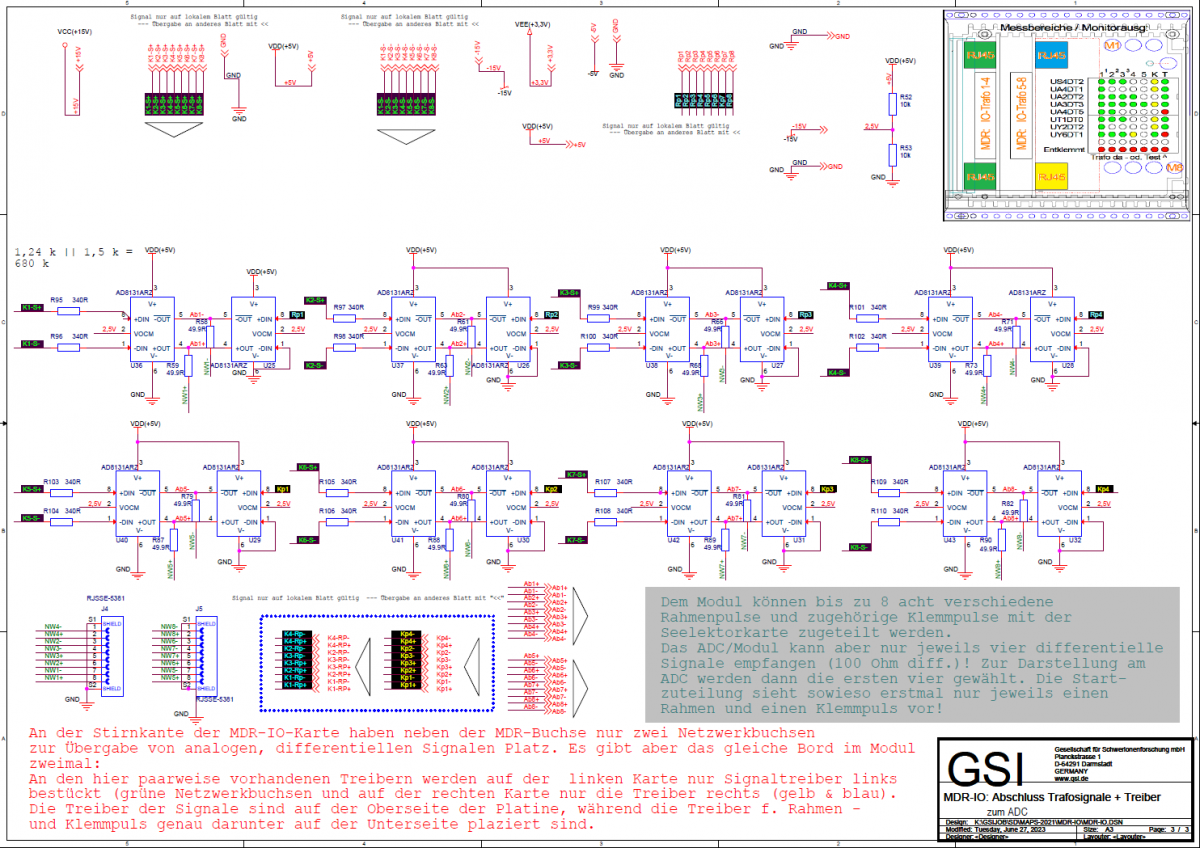

Die vier Steuerbits für vier Trafos kommen an der gleichen Stelle auf DER EINEN MDR-Buchse pro Karte an, haben aber acht verschiedene Zieltrafos: Alle 32 Steuerbits und 8 Klemmpulse mit CMOS-Pegel werden an der linken MDR_IO-Karte1) nach hinten abgegeben und laufen dort somit auch zusammen. Sie werden aber auf beiden MDR-IO-Karten, links und rechts2) generiert. Diese Steuerbits werden im Platinenstapel des HF-Modules von der “Displaycontrol”-Karte zur Darstellung ausgewertet und müssen daher alle auch auf den seitlichen VG-Leisten komplett vorhanden sein. Der Querschluss von Signalen von den zwei verschiedenen Quellen auf die gleich layouteten Platine, aber zweifach eingesetzt, wird dadurch vermieden, dass die Treiber entweder nur für die ersten vier Kanäle oder nur für die zweiten vier Kanäle bestückt werden! Die acht Treiber für die acht Trafos müssen in jedem Fall vorhanden sein.

An die DAC-IO-Karten gehen umgekehrt die “Trafo-da”-Signale über Zweiwegejumper für die ersten vier Trafokanäle auf die Treiber 1-4 geschaltet und auf dem oberen Board zu den Kanälen 5-8!

Die Pfostenwanne “J14” dient der Kommunikation des MAPS-Adapters mit dem DAQ-IO im µTCA-Crate und wird nur auf der rechten (oberen) Platine bestückt: Sie kommuniziert am Adapter lokal angewählte Wunschmessbereiche und den Index des dazu angewählten Trafo an das IO. Das Signalvolumen der Seiten VG gibt das nicht mehr her. Die Signale werden demzufolge nur auf der rechten IO ausgewertet.

Die Spannungsüberwachung der Teilspannungen erfolgt wie in den Vorgaben angefordert modulweise, da diese auch modulweise abgesichert sind.3) werden die anderen nicht betroffen bleiben.

★ Pegelwandler S1 ★ Rahmenpuls ★ Signalbuffer ★ Monitorbuffer ★ IO-Belegung ★

Seite 2 - Rahmenpuls & Klemmpuls (Rechte Karte)

Seite 3 - Signal (Links) - Timing (Rechts)

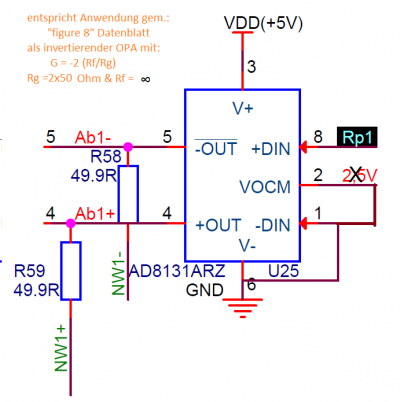

Auf dieser Seite werden die Orginaltrafosignale 680 Ω abgeschlossen und mittels Treibern 100 Ω-differentiell zu den ADCs über zwei RJ45 Buchsen gestellt. Die abgebufferte Halbsignale heißen “AB+/AB-”, zur Ausgabe an die DAQ an Netzwerkbuchsen dann “NW+/NW-” hinter den 50Ω-Widerständen. Erstere werden auch quer abgegriffen zum Erzeugen von single ended Monitorsignalen. Diese sind bisher zur Abgabe von +/-1V vorgesehen, könnten aber nach oben skaliert werden (+/-10V) wenn hochohmig abeschlossen (Simulation Funktion eines Differentellen Buffers):

Die beiden MDR-IO-Karten eines Modules werden alternativ bestückt je nach Einsatzort: Linke Karte Trafosignaltreiber (grün) — Rechte Karte Rahmen- (blau) und Klemmpulse (gelb). Da die Pulssignale auf dem rechten Board ebenfalls über die gleichen Netzwerkbuchsen den ADCs zugeführt werden, besitzen Ihre Abgänge die gleichen Signalnamen “Ab+” / “Ab-” und “NW+” / “NW-”. Einen Signalkonflikt an diesem T-Punkt gibt es nicht, da hier die Treiber für die analogen Signale unbestückt bleiben. Im gepunkteten Rahmen befinden sich die deswegen die nicht benutzet Signalnamen.

Leider gibt es in diesem Teilschaltplan einen fehlerhafte Lücke, der sich ins Layout fortpflanzt: Halb rechts oben sieht man einen Schaltplanblock, indem die Signale des Rahmenpulses (zyan) auch diesem Teilblatt zugeführt werden. Hier fehlt der gleichartige Teil für die Übergabe der single ended Klemmpulssignale. Das wird im Layout durch vier Drahtverbindungen korrigiert!

s.a.: Netzwerkkodierung

★ Pegelwandler S1 ★ Rahmenpuls ★ Signalbuffer ★ Monitorbuffer ★ IO-Belegung ★

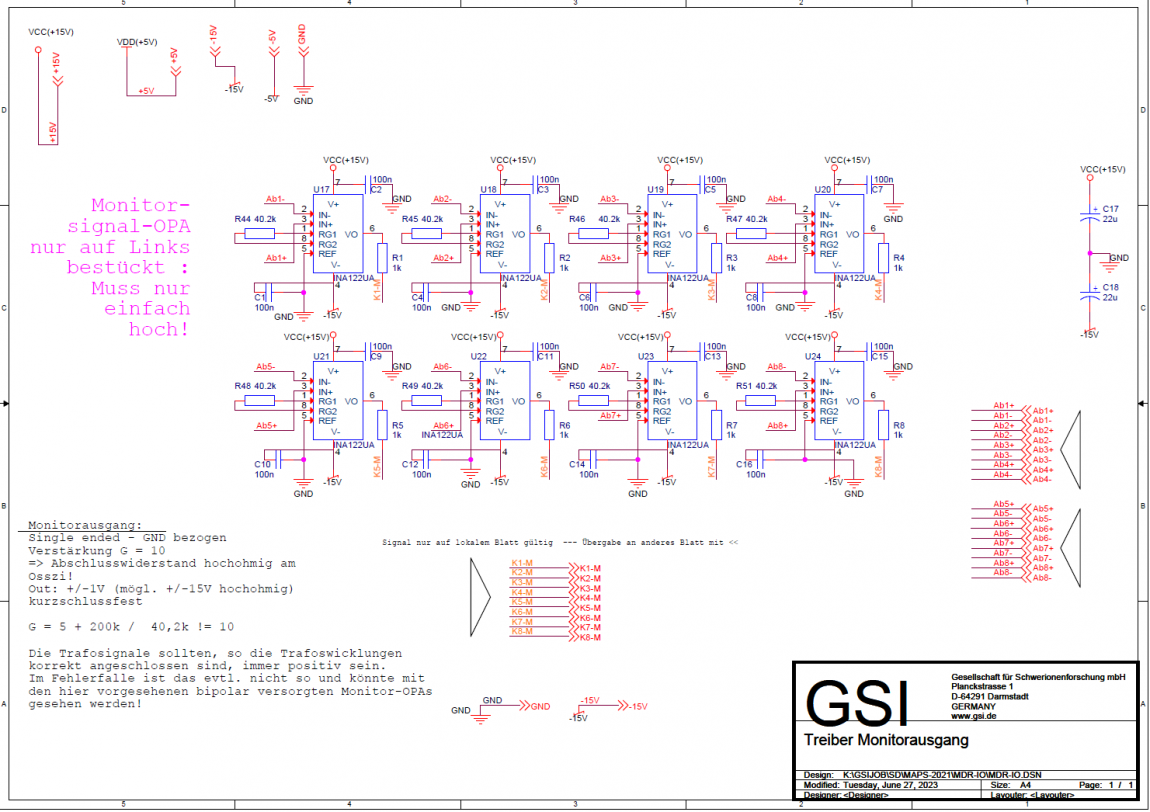

Seite 4 - Treiber Monitorausgang

Der Monitorausgang soll ein max. 10V-Signal auf einer 1pol. LEMO-Buchse single-ended, also auf Ground bezogen, zur Ausgabe bringen. Wenn alles stimmt sollte das positiv sein. Allerdings ist es möglich, dass das Trafosignal durch falsch Verlötung im Kopfverstärker oder umgekehrten Einbau des Trafos im Strahlengang negativ ist. Genau solche Fehlerfälle müssen mit dem Monitorausgang untersucht werden können! Die Ausgabe der Monitorsignale geschieht einerseits über das DisplayContrl-Board an frontseitigen LEMO-Buchsen und andererseits intern an eine 16pol. Pfostenwanne: So kann ggf. auf Nutzerwunsch dieses Signal an einem seperaten 3HE-Einschub für “Osszikunden” vervielfältigt werden. Der Frontseitige Monitorausgang bleibt dem Servicepersonal von BEA vorbehalten!

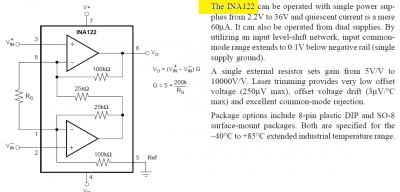

pdf \\################################################################################################################## \\################################################################################################################## | Achtung: Der Ursprünglich im Schaltplan vorgesehenene Instrumentierverstärker INA188D war nur sehr langfristig zu beschaffen und wurde durch einen Anschlussgleichen INA122UA ersetzt! Dies bedingt allerdings eine andere externe Widerstandsbestückung, um das die gleiche Zielverstärkung von G =10 zu erzielen! Der Schalplan wurde entsprechend adaptiert! |

★ Pegelwandler S1 ★ Rahmenpuls ★ Signalbuffer ★ Monitorbuffer ★ IO-Belegung ★

festgestellte Schaltplanfehler

| Pos. | Kurz | Beschreibung | Fehlerbehandlung |

|---|---|---|---|

| 1 | Keine “-15V” Überwachung | Die modulweise auf die DAQ-IO gestellten Überwachunghsbits sind dort nicht feststellbar: Der Optokoppler invertiert das Signal, daher läßt die präsente -15V-Spannung die LED durch Stromfluss leuchten, der sekundärseitige Transistor schaltet die Kontrollspannung auf GND und damit logisch “L”. R54 ist leider nicht an 3,3V angeschlossen, s.a. nächster Punkt. | Inversion in HBs Software. |

| 2 | Keine 3,3V Spannungsüberwachung | Die modulweise auf die DAQ-IO gestellten Überwachungsbits sind dort nicht feststellbar! Die 3,3V-Versorgung auf dem Board sollte erfolgen durch eine nicht durchgerootet Leiterbahn. Diese endet mit einem Via neben dem unteren Pad von C17! Somit fehlt 3,3V zwischene R41 und R54! | Ersatzdrahtbrücken! |

| 3. | 4,5V statt 3,3V? | liefert der unbelastet 3,3V Regler eine höhere Leerlaufspannung? | checken! |

| 4. | An U25 ist Pin 1 nicht wirklich mit Pin 6 mit GND verbunden: | Der Verbindungspunkt im Schaltplan fehlt - der wire sollte nicht verbunden sein, ist es aber wohl. U28 ist Pin1 tatsächlich nicht geroutet! | Brücke löten |

| 5. | Klemmpulse nicht an dritte Schaltplanseite übergeben!4): Keine Kps über Buffer (U29-U32) an ADCs zum Aufzeichnen. | Die Klemmpulse sind zwar über die VG-Leiste als Ganzes der Karte zugeführt, durch die zur Übersichtlichkeit eingeführte Aufteilung auf verschieden Schaltplanseiten wurden hier die Signale nicht übernommen wie bei den Rahmenpulsen: Die Übergabe von Signal “Kp”x hätte mit dem “»”-Operatoren an “» KP” x erfolgen sollen! Möglichkeit d. Fehler: Die Klemmpulssignale, bisher in das Modul geführt, sind die, die für die acht hinten angeschlossenen Trafos vorgesehenen sind. Liegen die alle in der gleichen Zone, wird weniger als möglich an die einzige Netzwerksbuchse zur Aufzeichnung von vier Klemmpuls-Kanälen weitergeben. Werden stattdessen die ersten vier rückwärtigen Eingangssignale aufgelegt, also vor der Pfostenwanne zum Selektor, so können auch verschieden Klemmpulse erfasst werden!5) | Ersatz durch: Drahtbrücken! oder Flachband |

| 6. | Ausgangs Common Mode Offset für Trafosignal an ADC | Der Ausgang der Analogsignalbuffer AD8132 ist hier nicht bipolar versorgt, sondern GND-bezogen: dadurch muss der Buffer eine positive Common Mode Mitte vorgeben, um darum ein differentielles Ausgangssignal zu generieren! Das geht zwar prinzipiell, aber besser ist auch am Ausgang symetrisch um Null zu bleiben, um nicht an die Eingangspollerspannungen des ADCs zu stoßen. | -5V aus -15 generieren in MDR-IO-V2! |

| 7. | Kein Feedback — kein 1:1 | Es fehlen zur Bufferung mit 1:1 Verstärkung die externen Feedbackwiderstände zwischen den Eingängen und den Ausgängen! | Korrektur in V2! |

| 8. | Keine 2,5V Offsetvorgabe für die Bufferausgänge | Die Vorgabe eines Ausgangsoffset von 2,5V an den Bufferbausteinen durch Vorgabe an den Eingang ist nicht sinnvoll. Zuviel Hub! | Hier nicht vollstädig geroutetets Signal 2,5V an GND-Fläche korrigiert — In V2 die Pins 2 an GND binden! |

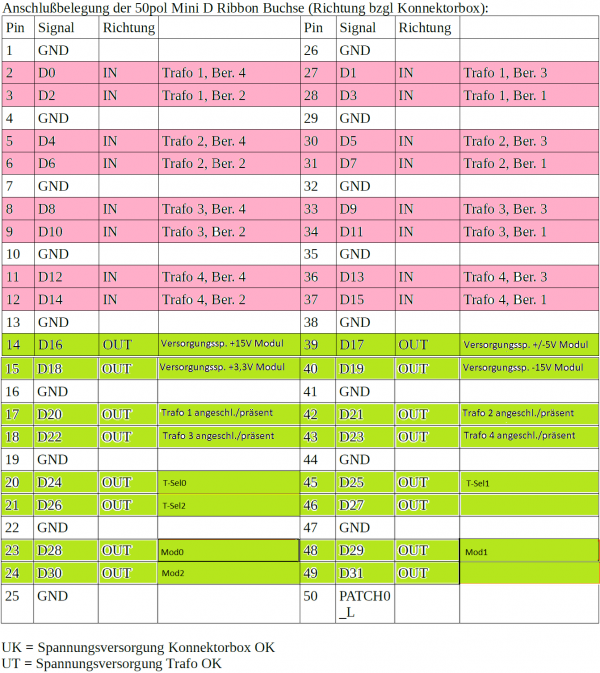

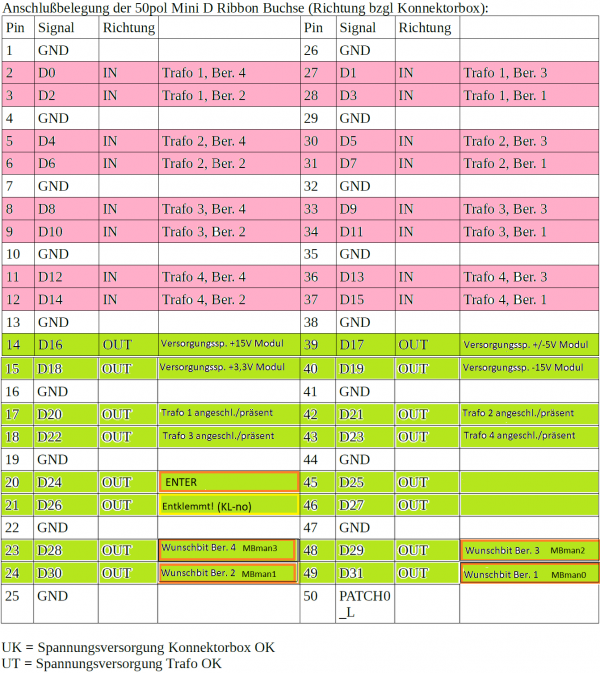

Erweiterte IO-Belegung

Bezogen auf den Adaper (nicht IO-Karte):

Die orange und gelb gerahmten Signale werden auf der MDR-IO-Karte rechts für die Kanäle 5-8 vom Displayboard übernommen.

★ Pegelwandler S1 ★ Rahmenpuls ★ Signalbuffer ★ Monitorbuffer ★ IO-Belegung ★

☚ Schaltungen ★