Wiki

User Tools

Sidebar

Table of Contents

☚ Schaltungen ★

| hinten >>>>>>>>> vorne | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||

| Schaltungen: | | | | | Front | Selektor | Q+D | Signaltransfer über alles |

|

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | X | |||

| Layouts: | | | | | Front | Selected | Q+D | ||

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | MDR-IO-V2 | |||

### Bestellt und in Herstellung (Leiterkarte) ### Ersetzt!

MDR-IO-V2

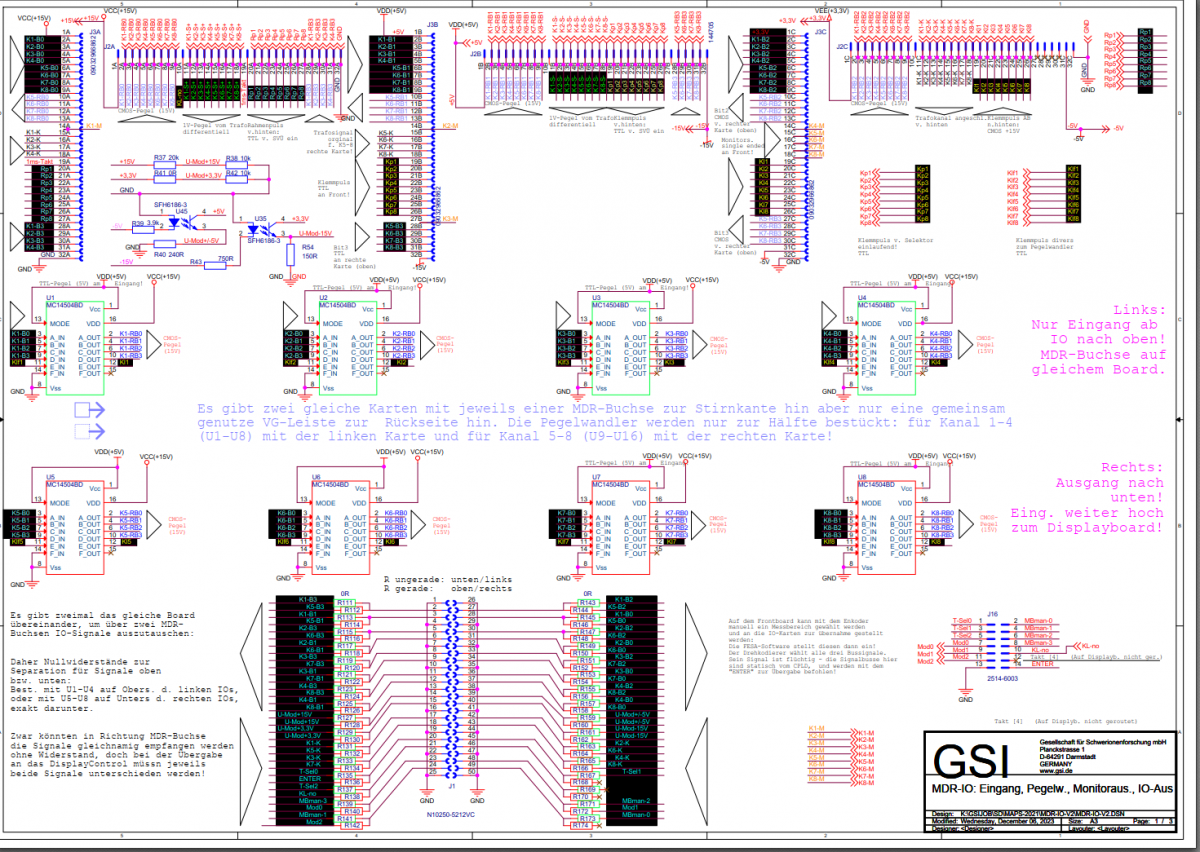

Seite 1 - Pegelwandler-IO

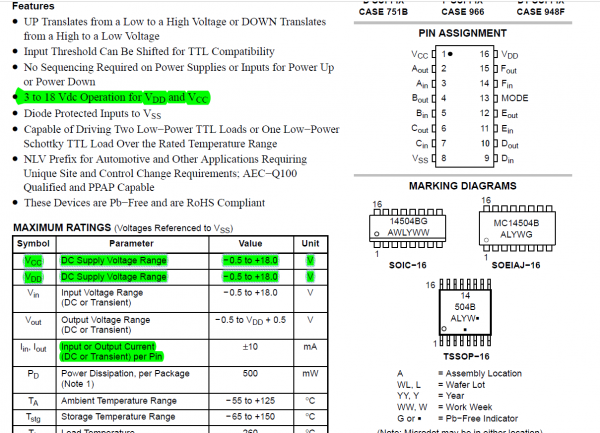

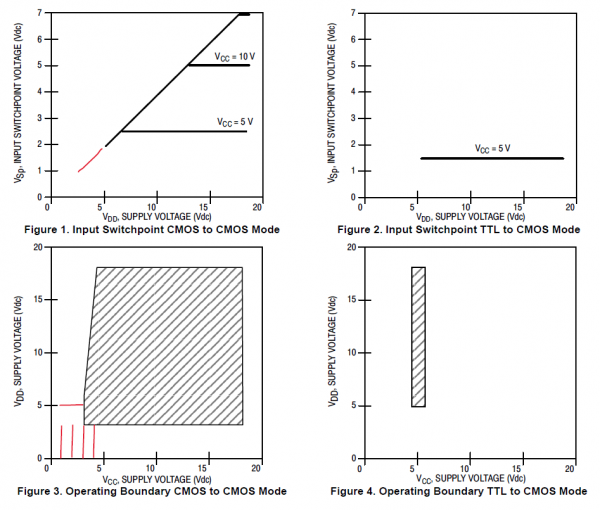

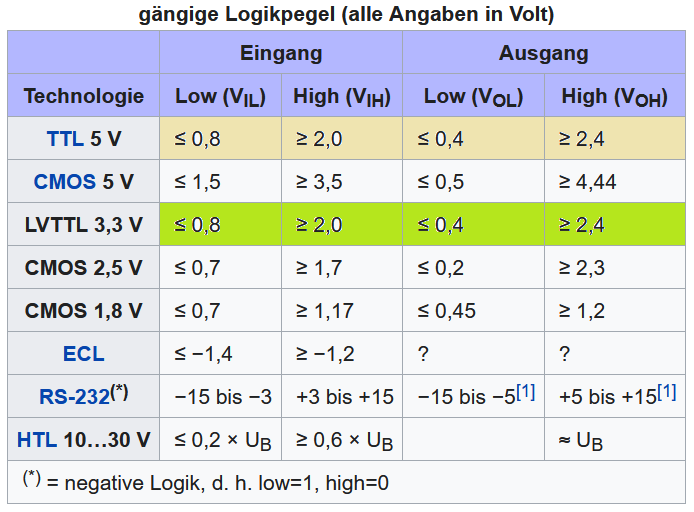

Mit hinterer VG-Leiste und seitlicher VG-Leiste zur Frontplatte. Die erste Seite enthält zweistufig Pegelumsetzer von LVTTL (IO) → TTL (Anzeige) → CMOS (15V) für die Trafos.

Pegelerörterung

Die von den DAC-IOs gestellten Steuerpegel sind LVTTL 3,3V — die Trafos benötigen CMOS 12-15V! Die Pegelwandlung mit dem vorgesehenen Baustein erfolgt einstufig.

Schaltpläne

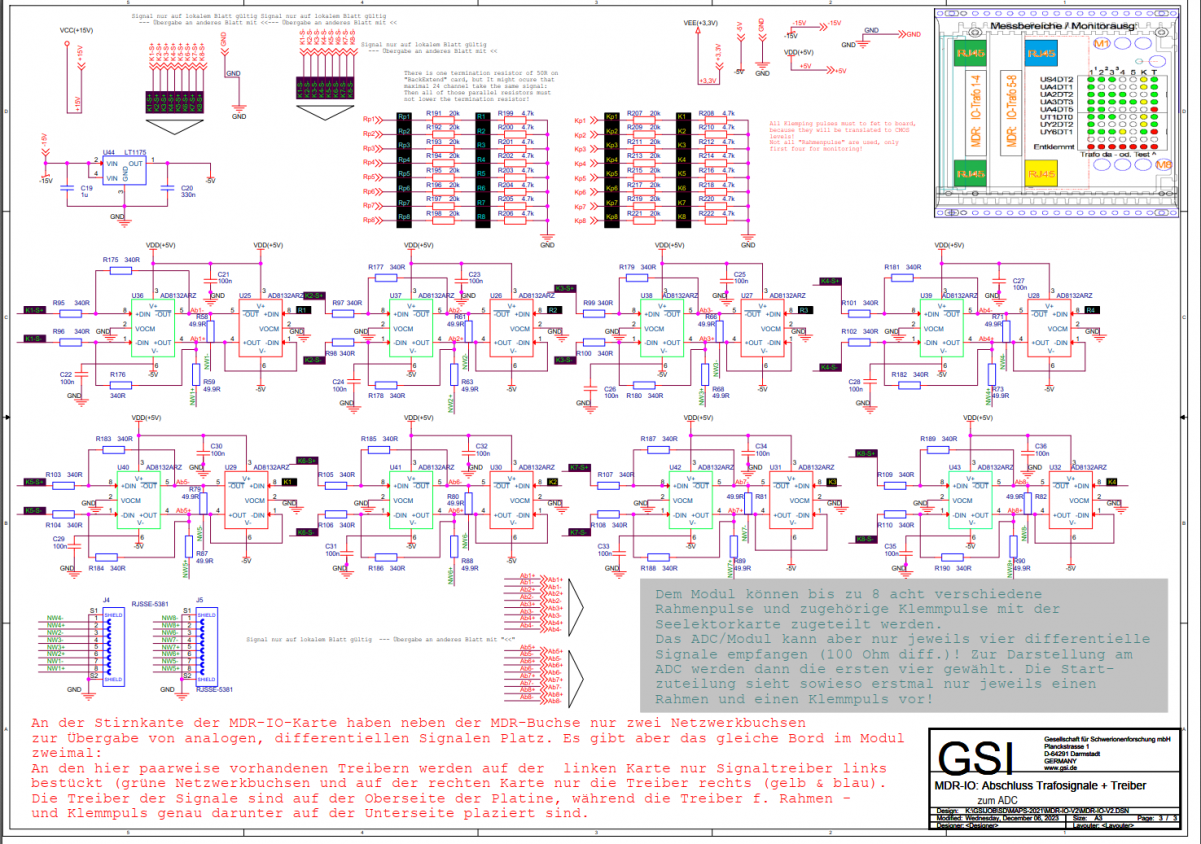

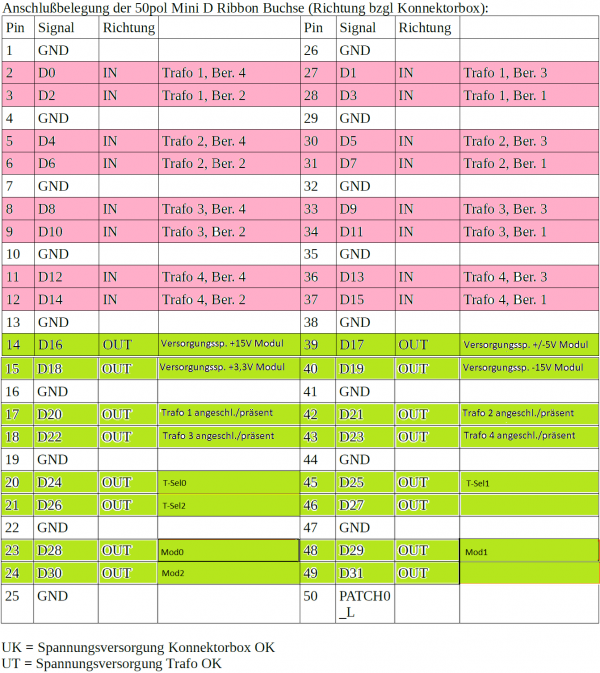

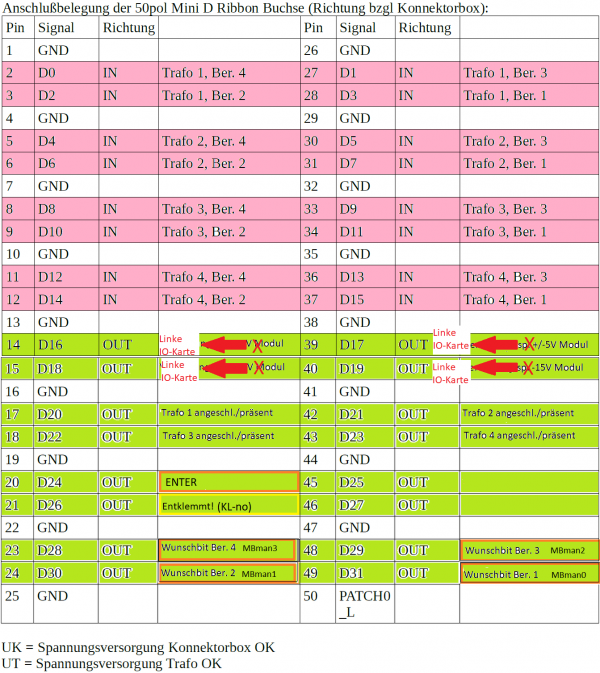

Die vier Steuerbits für vier Trafos kommen an der gleichen Stelle auf DER EINEN MDR-Buchse pro Karte an, haben aber acht verschiedene Zieltrafos: Alle 32 Steuerbits und 8 Klemmpulse mit CMOS-Pegel werden an der linken MDR_IO-Karte1) nach hinten abgegeben und laufen dort somit auch zusammen. Sie werden aber auf beiden MDR-IO-Karten, links und rechts2) generiert. Diese Steuerbits werden im Platinenstapel des HF-Modules von der “Displaycontrol”-Karte zur Darstellung ausgewertet und müssen daher alle auch auf den seitlichen VG-Leisten komplett vorhanden sein. Der Querschluss von Signalen von den zwei verschiedenen Quellen auf die gleich layouteten Platine, aber zweifach eingesetzt, wird dadurch vermieden, dass die Treiber entweder nur für die ersten vier Kanäle oder nur für die zweiten vier Kanäle bestückt werden! Die acht Treiber für die acht Trafos müssen in jedem Fall vorhanden sein.

An die DAC-IO-Karten gehen umgekehrt die “Trafo-da”-Signale über Zweiwegejumper für die ersten vier Trafokanäle auf die Treiber 1-4 geschaltet und auf dem oberen Board zu den Kanälen 5-8!

Die Pfostenwanne “J14” dient der Kommunikation des MAPS-Adapters mit dem DAQ-IO im µTCA-Crate und wird nur auf der rechten (oberen) Platine bestückt: Sie kommuniziert am Adapter lokal angewählte Wunschmessbereiche und den Index des dazu angewählten Trafo an das IO. Das Signalvolumen der Seiten VG gibt das nicht mehr her. Die Signale werden demzufolge nur auf der rechten IO ausgewertet.

Die Spannungsüberwachung der Teilspannungen erfolgt wie in den Vorgaben angefordert modulweise, da diese auch modulweise abgesichert sind.3) werden die anderen nicht betroffen bleiben.

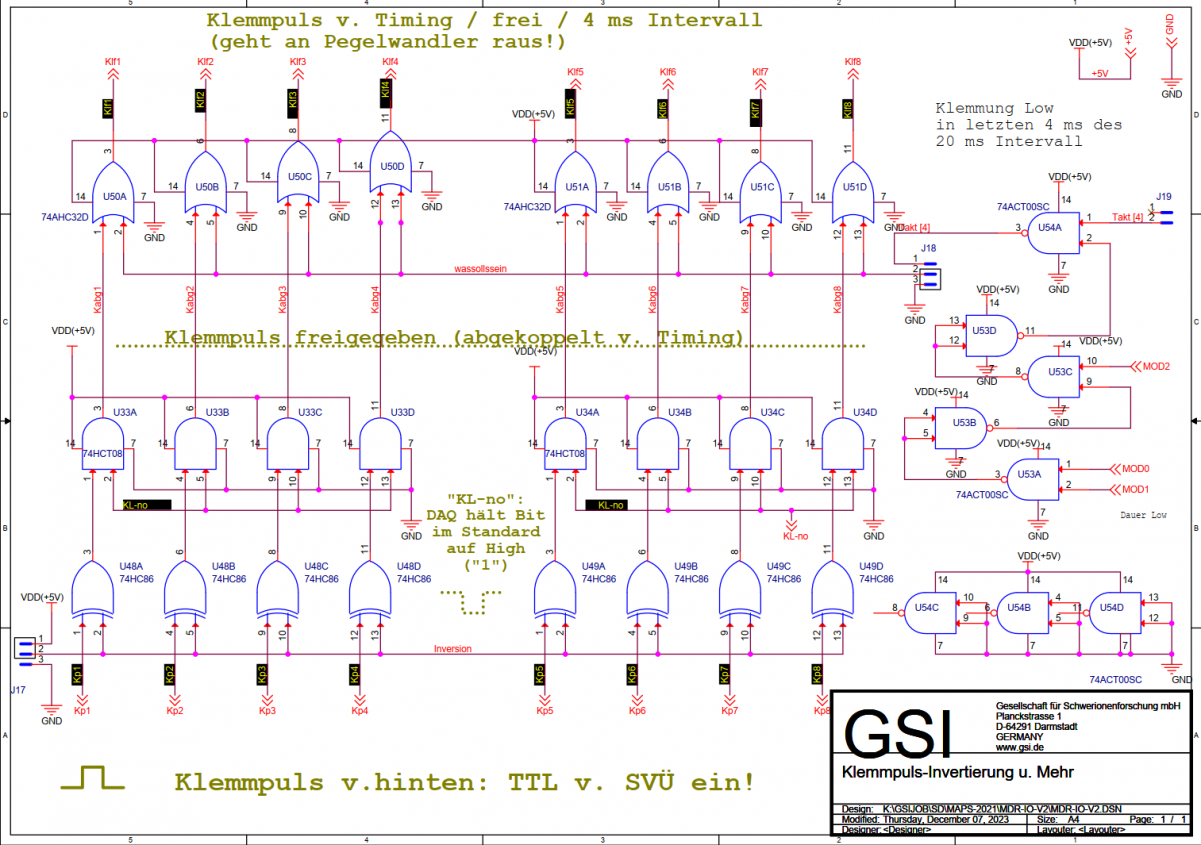

Seite 2 Klemmoptionen

Es kann ab der Selektorkarte prinzipiell für jeden der acht Trafos ein eigener Klemmpuls gewählt werden. Mit dem Zweiwege Jumper kann nun so für alle gemeinsam das positive Signals ab Controls eine gleichartige Weitergabe oder aber eine Inversion der Klemmpulse erzielt werden: Die Kopfelektroniken benötigen inverse Pulse.

Weiter gibt es eine Option (Mode 7), mittels des Drehwahlschalters der Software den Wunsch mitzuteilen, einen oder mehrere Trafos von der Beschleunigervorgabe abzu koppeln und die Kopfverstärker zu entklemmen: auf diese Weise ist eine Erfassung der Trafopulse am Monitorausgang mit dem Osszy dann möglich!

Eine weitere Variante dabei wäre der Zugriff auf eine Klemmung aus den letzten 4 ms der UNILAC Intervalle zu nutzten. Die Standard Position des Jumpers ist aber zunächst die komplette Freigabe der Klemmung.

Die drei Bits des MODE-Buses MODE[0..2] werden mit dem Drehwahlschalter angewählt und der MODE#7 durch Drücken aktiviert. Das DAQ-IO registriert diese Anfrage und kann dann, wenn es passt, das “KL-no” Bit auf Low ziehen: das Operating wird das in der Steuer-Software freigeben, da der Wunsch, einen potentiell fehlerhaften Trafo zu prüfen ja auch dort seinen Ursprung hat.

Timing letzte 4ms UNILAC

Die zwanzig 1 ms-Takte im 50 Hz/ 20ms-Takt werden gezählt, von jeder Periode neu getriggert synchronisiert zur grundlegenden Stromphase. Die letzten 4ms beinhalten immer potentiell Strahl und bieten so ein Beschleunigerunabhängiges, UNILAC synchrones Timing. Die Klemmung ist low active (Beige)!

Seite 3 - Rahmenpuls & Klemmpuls (Rechte Karte)

Seite 3 - Signal (Links) - Timing (Rechts)

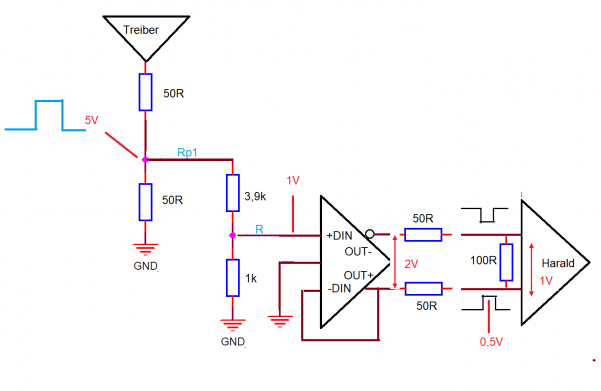

Auf dieser Seite werden die Orginaltrafosignale 680 Ω abgeschlossen und mittels Treibern 100 Ω-differentiell zu den ADCs über zwei RJ45 Buchsen gestellt. Die abgebufferte Halbsignale heißen “AB+/AB-”, zur Ausgabe an die DAQ an Netzwerkbuchsen dann “NW+/NW-” hinter den 50Ω-Widerständen. Erstere werden auch quer abgegriffen zum Erzeugen von single ended Monitorsignalen. Diese sind bisher zur Abgabe von +/-1V vorgesehen, könnten aber nach oben skaliert werden (+/-10V) wenn hochohmig abeschlossen (Simulation Funktion eines Differentellen Buffers):

Die beiden MDR-IO-Karten eines Modules werden alternativ bestückt je nach Einsatzort: Linke Karte Trafosignaltreiber (grün) — Rechte Karte Rahmen- (blau) und Klemmpulse (gelb). Da die Pulssignale auf dem rechten Board ebenfalls über die gleichen Netzwerkbuchsen den ADCs zugeführt werden, besitzen Ihre Abgänge die gleichen Signalnamen “Ab+” / “Ab-” und “NW+” / “NW-”. Einen Signalkonflikt an diesem T-Punkt gibt es nicht, da hier die Treiber für die analogen Signale unbestückt bleiben. Im gepunkteten Rahmen befinden sich die deswegen die nicht benutzet Signalnamen.

| s.a.: Netzwerkkodierung s.a.:  | Die Aderpaare sind NICHT sequentiell auf die Netzwerbuchsenpins aufgelegt. Dies ist bedingt durch die Anordnung der Adern im Kabel mit ihren paarweisen Schirmen! |

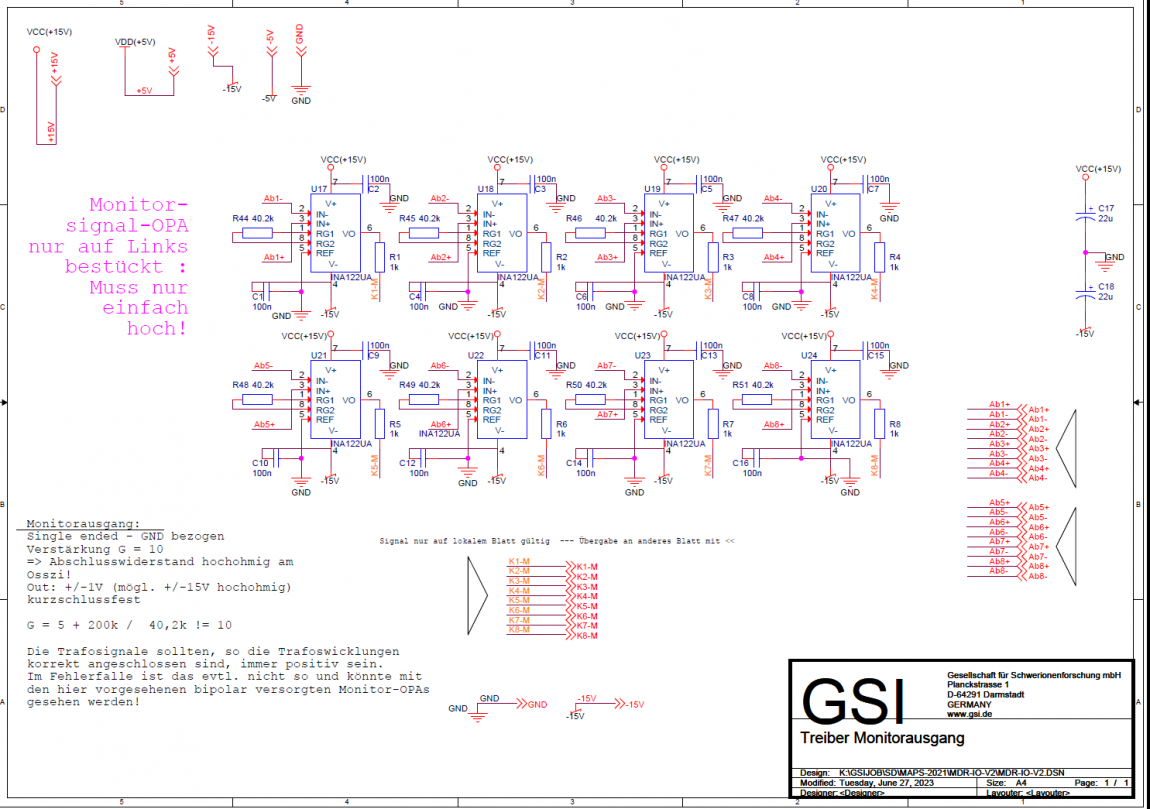

Seite 4 - Treiber Monitorausgang

Der Monitorausgang soll ein max. 10V-Signal auf einer 1pol. LEMO-Buchse single-ended, also auf Ground bezogen, zur Ausgabe bringen. Wenn alles stimmt sollte das positiv sein. Allerdings ist es möglich, dass das Trafosignal durch falsch Verlötung im Kopfverstärker oder umgekehrten Einbau des Trafos im Strahlengang negativ ist. Genau solche Fehlerfälle müssen mit dem Monitorausgang untersucht werden können! Die Ausgabe der Monitorsignale geschieht einerseits über das DisplayContrl-Board an frontseitigen LEMO-Buchsen und andererseits intern an eine 16pol. Pfostenwanne: So kann ggf. auf Nutzerwunsch dieses Signal an einem seperaten 3HE-Einschub für “Osszikunden” vervielfältigt werden. Der Frontseitige Monitorausgang bleibt dem Servicepersonal von BEA vorbehalten!

pdf \\################################################################################################################## \\################################################################################################################## |

Hinweise Schaltplan

![]()

| Pos. | Kurz | Beschreibung | Fehlerbehandlung |

|---|---|---|---|

| 1. | Monitorverstärkung zu gross | Verstärkung 10 ist zu groß, da sie nicht auf die einfache Amplitude 1V, sondern das Δ= 2V, die Differenzspannung wirkt. | Position von 40,2 kΩ Verstärkungswiderstand nicht bestücken! |

| 2. | K1-4 Trafo präsent nicht zum Display | Im Schaltplan gehen die Signale nur fast an die VG-Leiste nach oben: das Display kann die Signale nicht darstellen. Zum IO der DAQ gehen sie aber! | |

| 3. |

Erweiterte IO-Belegung

Bezogen auf den Adaper (nicht IO-Karte):

Die orange und gelb gerahmten Signale werden auf der MDR-IO-Karte rechts für die Kanäle 5-8 vom Displayboard übernommen.

★ Pegelwandler S1 ★ Rahmenpuls ★ Signalbuffer ★ Monitorbuffer ★ IO-Belegung ★

☚ Schaltungen ★

![Takt[4] Takt[4]](/dokuwiki/lib/exe/fetch.php?w=1000&tok=dea80d&media=projects:maps21:s:mdr2:timing_takt_4_.png)