Wiki

User Tools

Sidebar

This is an old revision of the document!

Table of Contents

☚ Schaltungen ★

| hinten >>>>>>>>> vorne | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | |||||

| Schaltungen: | SubDback | BackExtend | MDR-IO | DisplayContr | Front | Selektor | Q+D | Signaltransfer über alles | ||

| Layouts: | SubDback | BackExtend | MDR-IO | DisplayContr | Front | Selected | Q+D | |||

Board Display Control

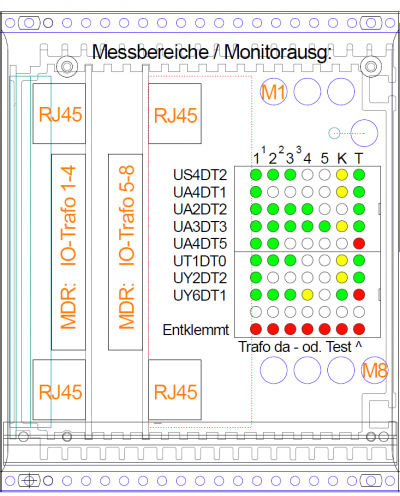

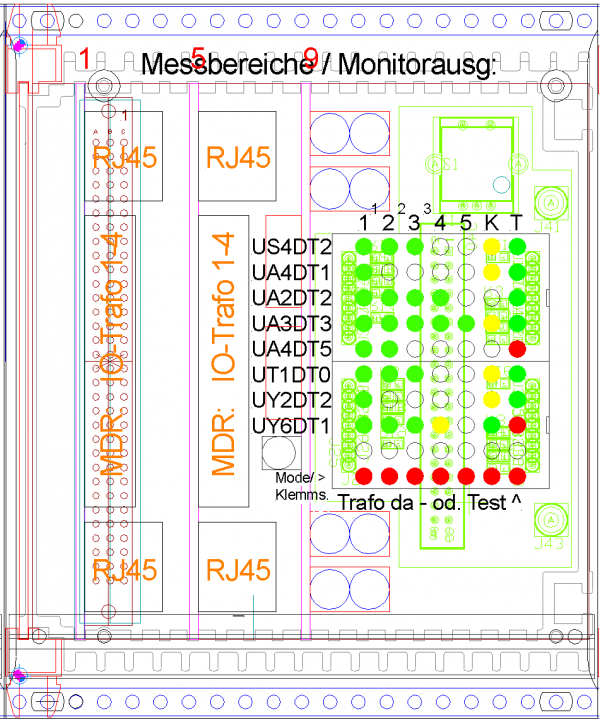

Dieses Board “DisplayContr-V1” ist der “MDR-IO”-Platine an der internen VG-Leiste aufgesetzt und beherbergt Treiber und Kontrollogik, die auf der Frontseite mit dem Matrixelement räumlich nicht unter zu bringen ist. Diese Platine ist also parallel zum Mutterboard angeordnet. Das Display an der Frontplatte ist orthogonal an der Frontplatte und ist dann per Flachbandkabel dem “DisplayContr-V1” verbunden! Die Anzeige des Matrixelementes stellt dem Wartungspersonal des Trafofrontends wichtige Informationen im Problemfall zur Verfügung! Es kann damit auch gezielt mittels der Monitorausgänge das Trafosignal am Osszyllloskop betrachten. Die auf diese Ebene aufgesetzte Ebene der FESA-Softwareerfassung basiert auf diesem Adapter und funktioniert nur korrekt solange eben kein Fehler vorliegt. Deswegen ist die Visualierung der Trafoanzeige auf dem Display elementar wichtig!

Schaltplan "DisplayContr-V1"

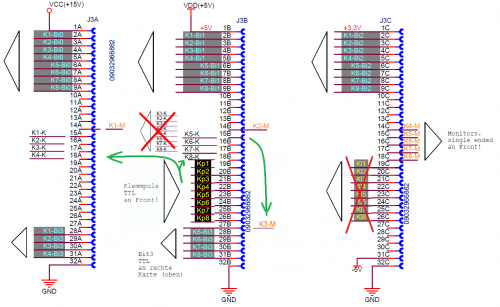

Page 1 Umfeld Plt.

Das DisplayControl board steuert mittels zweier CPLDs die Darstellung der Messbereiche und Klemmpulse in Echtzeit auf der LED-Anzeige. Dies “lebt” im 50 Hz UNILAC-Takt (Abbildung).

notwendige Korrekturen: <white/white>################################################################################</color> | Im umgesetzten Schaltplan unten sind einige Signale nicht an die Gegebenheiten des Mutterboards unten angepasst: Die “Trafo-angeschlossen-Signale” sind oben nicht zu übernehmen: von unten liegen die Klemmpulssignale der Rückfront an! Auch Monitorsignal “M3” liegt falsch. Erstere Signale müssen an die mit grünen Pfeilen bestimmten Positionen. Die vom Selektor gewählten Klemmpulse werden bereits mit CMOS-Pegeln von unten hoch geschickt: Das ist zuviel für die CPLDs. Daher werden diese Pulse heruntergeteilt! |

p1-pdf |  |

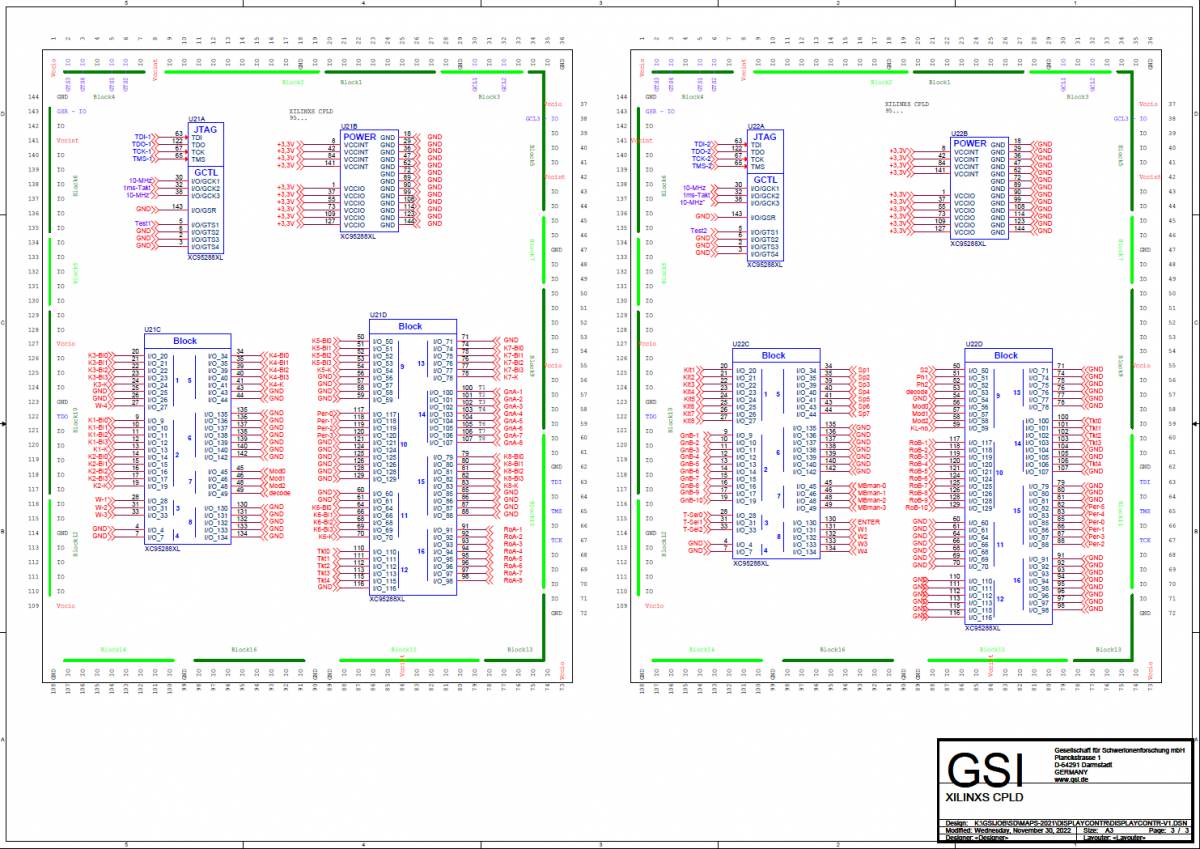

Page 2 XILINX CPLD

Die unten gezeigten Schaltsymbole dienen nur als Hilfskonstrukt, bis die EE korrekte Symbole für den eingesetzten CPLD angelegt hat: die Baugröße des abgebildeten Symbols ist mit der des Chips übereinstimmend und ermöglicht so das Layout! Die Pin-Nr-Funktionspaare am Symbol sind somit irrelevant.

Die gesamte page2 wird später durch mit dem korrekt angelegte Symbol ersetzt.

Die beiden CPLDs auf dem Board steuern den Ablauf der Ansteuerung des Punktmatrixelements im Milisekundentakt: Beide CPLDs haben Zugriff auf die grünen und roten LEDs des Elementes, um damit die drei möglichen Farben Rot, Gelb und Grün der Anzeige zu erzeugen. Grob beschrieben steuert der eine CPLD die Messbereichsanzeige in Grün und der andere CPLD die Klemmpulsanzeige in Gelb. Die Nutzung des Punktmatrixelementes reduziert den Stromverbrauch der LEDs, da in einem Augenblick immer nur eine Spalte des Displays zur Anzeige aktiv ist und stellt Messbereiche und Klemmung quasi live im 50Hz-Zyklus, 20 ms-Intervall dar: Die ersten 15ms im 20ms-Takt dienen der Strahlvorbereitung — die letzten 5ms stehen maximal dem Strahl zur Verfügung. Die im 50Hz-Takt vorgegebenen Messbereiche werden mit der 14. Millisekunde getastet und gespeichert (40 Bit), die Anzeige zweimal im Intervall komplett durchlaufen, bzw. erneuert.

Über einen Drehenkoder auf dem Frontboard können verschiedene Anzeigemodi angewählt werden (3Bit), durch Leuchten der ersten LED in grün für Modus “1” in der Zeile “Entklemmt”, der zweiten LED für Modus “2” usw.:

q

Anzeigemodi

- Standardmodus : Die Messbereiche werden dekodiert als Balkenanzeige mit 1-5 LEDs dargestellt, was den Aussteuerungsvergleich klarer macht! Der Klemmpuls wird Gelb und nur in der 6. Spalte des Displays angezeigt. Dabei ist die Anzeige transparent, d.h. jeder folgende Milisekundentakt mit Strahl wird an dieser Stelle angezeigt, die Anzeige leuchtet dann für das Auge des Betrachters intensiver, wenn die maximalen 5ms Strahl anstehen und schwächer wenn beispielsweise der Strahlpuls unter einer Millisekunde lang ist!

- Binäre Anzeige: dort werden die Messbereichsbits in ihrer digitalen Form dargestellt, so wie sie an den Trafo gehen. Das ist in einem potentiellen Fehlerfall hilfreich!

- Fokusmodus : mit dem Drehwähler wird die erste Aussteuer-LED eines Trafos gewählt und mit dem Fokus belegt per Drucktaster des Enkoders, d.h. sie wird von Grün auf Rot gestellt. Damit wird die Anzeige dieses eines Trafos statisch, damit dort die Anzeige für den menschlichen Beobachter besser dauerhaft erfasst werden kann. Welcher der zehn aufeinanderfolgenden 10 Intervalle von 20ms zur Darstellung gebracht wird, wird mit dem Drehkodierer nach Wahl des Trafos in der siebten Spalte für “Test” ausgewählt und durch Drücken der Enkoder Taste fixiert (4 Bit). Der Modus wird verlassen, wenn der Drucktaster auf dem mit Fokus belegtem Trafo erneut getätigt wird!

- 5ms-Klemmpuls: Hier wird der Klemmpuls aller fünf potentiellen Milisekundenintervalle mit Strahl in den Spalten 2-6 überblendet in gelb angezeigt. Also hier nicht nur in Spalte 6! Dabei werden grüne MB-LEDs evtl. gelb überblendet.

- Klemmpulsdauer: Hier wird das Vorhandensein des Klemmpuls in den maximalen fünf Millisekundentakten in Spalte 2 bis 6 dargestellt für einen ausgewählten Trafo im Fokus und für zehn aufeinaderfolgende 50 Hz-Takte in den zehn Zeilen dargestellt. Der Trafo wird mit dem Drehenkoder ausgewählt, mit dessen Drucktaste fixiert. Auf diese Weise kann die “parallele” Ansteuerung durch verschiedene aufeinanderfolgende virtuelle Beschleuniger, z.B. durch Hochladungsquelle und Hochstromquelle überprüft werden.

- Messbereich manuell : Ein Messbereich wird in der siebten Zeile ausgewählt und mit Drücken des Enkoders gesetzt. Die ausgewählten Ansteuerung wird dem IO-Board angezeigt. Die laufende FESA-Software registriert den Wunschsetzbereich und schaltet diesen auf alle acht (?) Kanäle des Modules. Dies hat den Vorteil, dass die laufende Remotesoftware den Steuervorrang hat und das Setzen eines Messbereichs zu Servicezwecken auch aus der Ferne wieder aufheben kann!

- Entklemmt : Hier wird die Klemmung, wie durch das Timing vorgegeben“, deaktiviert — die Kopfelektronik zur Dauermessung frei gegeben. Das Trafosignal kann dann auf dem Monitorausgang mit dem Osszi “gesehen” werden, auch wenn die Klemmung vom Kontrollsystem eben nicht richtig gesetzt ist und so eine sichtbares Trafosignal unterdrückt! Das sollte natürlich nicht zu lange geschehen, da der AC-gekoppelte Kopfverstärker ansonsten wegläuft.

- Phasenwahl: In diesem Modus ermöglicht der Drehgeber die Wahl einer Phasenverschiebung aus dem Intervall [ 0 ms, 19 ms]. Das UNILAC-Timing beruht auf der Netzfrequenz. Da gibt es allerdings drei mögliche Phasen im speziellen Rack für den 3HE-Einschub. Hier soll die einmalig die Wahl eines entsprechende Phasenshift ermöglicht werden.

- (Messbereichssequenz): In diesem Modus würden die Messbereichsvorgaben für einen Trafo für 10 aufeinaderfolgende 20ms-Intervalle dargestellt: das ermöglicht die Analyse der Vorgabe von Messbereichen durch das Kontrollsystem gemäß den virtuellen Beschleunigern! Wird zunächst nicht vorgesehen.

Aufgaben der beiden CPLDs

Der erste CPLD erfasst an 50 Eingängen die drei Messbereichsbits, die Testfunktion und das Bit für Kanal präsent. Diese fünf Bit können, aber müssen nicht unbedingt gespeichert werden, da sie nur der Anzeige auf dem Matrixelement dienen und nicht digital weiterverarbeitet werden.1). Werden diese Bits nicht gespeichert und nur zum relevanten Millisekundentakt durchgeschaltet, so wird das transparent genannt. Innerhalb einer Periode stehen zwanzig Milisekundenintervalle zur sequentiellen Aktivierung der sieben Spalten zur Verfügung — nicht 21!. Die Klemmunng in der 6. Spalte soll normalerweise transparent und live in den letzten 5 ms mit Strahl angezeigt werden: Deswegen werden nach Begin einer neuen Periode nur die Spalten 1,2,3,4,5 (MB-Balkenanz.) und 7 sequentiell aktiviert. Im Fall einer Speicherung werden 50 der 128 Bitspeicherstellen benötigt! Die Speicherung würde dann im 13. Takt erfolgen. Die Takte 14-20 würden darauf mit dem Strahl live dargestellt: dann auch der Klemmpuls in der 6. Spalte. Dieser erste CPLD führt auch die Dekodierung der drei Messbereichsbits zur Balkenanzeige hin aus. Der kontinuierlich bis 20 laufende Taktbus wird vom zweiten CPLD empfangen.

Der zweite CPLD zählt einerseits den Einlaufenden Millisekundentakt binär und gibt diesen Takt auf einen Taktbus “Tkt0-4” aus. Volle 20ms-Intervalle bilden einzelne Zeilen und werden als Perioden bis Fünfzig gezählt und auf den Bus “Per0-5” ausgegeben. Diese 50 Perioden in der Sekunde bilden die maximal möglichen Time slots für virtuelle Beschleuniger. Der CPLD erfaßt an acht Eingängen die anstehenden Klemmpulse der Trafos im Millisekundentakt mit Strahl (max. 5ms) und speichert diese ggf. für einen Trafo und die Darstellung in zehn Intervalle, also 200ms zwischen. Diese Speicherung des Klemmpulses in Einmillisekundenintervallen ist auch deswegen nötig, da es z.B. bei Strahlverkürzung auch Packete von nur 10µs geben kann. Dies zu erkennen wäre für den menschlichen Beobachter zu schnell! Dafür werden 50 Bit benötigt. Der durchlaufende Taktbus wird dekodiert in sieben Spalten: die jeweils zur Anzeige aktive Spalte des Displays. Der mittels Drehenkoder und interiertem Drucktaster gewählte Anzeigemodus wird auf den Modebus “Mod0-2” ausgegeben und intern gespeichert (3Bit). Der gewählte Mode wird als einzeln leuchtende LED in der untersten Zeile visualisiert. Ebenfalls wird durch den Drehentkodierer die Fokusselektion “W-1-4” als Bus ausgegeben und intern gespeichert (4 Bit): Dies selektiert entweder einen Trafo zur Handbedienung (Mode 5) in der ersten MB-Anzeigestelle rot oder die Zeile, also das Klemmpulstiming aus dem virtuellen Beschleuniger in der letzten Anzeige-LED gelb für Mode 4! Weiter wird der per Drehenkoder bestimmte manuelle Messbereich auf den Bus Man0-2 bitweise gemäß Rangecodierung ausgegeben.

Die meisten an die CPLDs übergebenen Signale entstammen quasi-statischen Quellen und müssen daher nicht entprellt werden. Dies gilt nicht für die Signale des Drehenkoders und seines Drucktasters. Sie müssen eventuell innerhalb des CPLDs elektronisch entprellt werden! Das benötigt dann die Reservierung einiger Speicherbits. Vielleicht in Form eines fünfstufigen Schieberegisters basierend auf den einlaufenden 1ms Takten an dem dann auf Vorhandensein von fünf aufeinaderfolgenden Einsen geprüft wird. Annahme dabei: übliches Kontaktprellen unter einer Millisekunde.

Das “Decode”-Signal ist die Übergabe Status “Schalter gedrückt” von einem CPLD zum Anderen, da der Schalter ja physisch zur Auswertung nur an einen verbunden ist, die Anwahl in den diversen Modi aber wohl auch vom zweiten CPLD verarbeitet werden muss!

Ggf. muss vom CPLD auch ein Phasenschift bezüglich des richtigen 50 Hz-Taktes ausgeführt werden: Das GSI-UNILAC-Timing basiert zwar auf auf dem Netzintervall, aber welche der drei Drehstomphasen am Rackstromanschluss vorliegt ist nicht klar.

Bedienkonzept

Der gedrehte Drehwahlschalter erweckt den Courser zum Leben: punktweise in der zehnten Zeile grün blinkend (hier komplett rot), wo durch Punkt der aktive Mode angezeigt wird! Druck des Drehwählers an einer Stelle, z.B. zweiter Position wählt dann diesen zweiten Mode, die LED leuchtet dauernd!

Code für CPLDs

Der VHDL-Code für die beiden CPLDs wird aktuell freundlicherweise von Rene Geissler umgesetzt und findet sich auf dem GIT Repository:

★ VHDL-Code-Seite ☛

☚ Schaltungen ★