☚ Schaltungen ★

| hinten >>>>>>>>> vorne | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||

| Schaltungen: | | | | | Front | Selektor | Q+D | Signaltransfer über alles |

|

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | X | |||

| Layouts: | | | | | Front | Selected | Q+D | ||

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | MDR-IO-V2 | |||

### Bestellt und in Herstellung (Leiterkarte) ### Ersetzt!

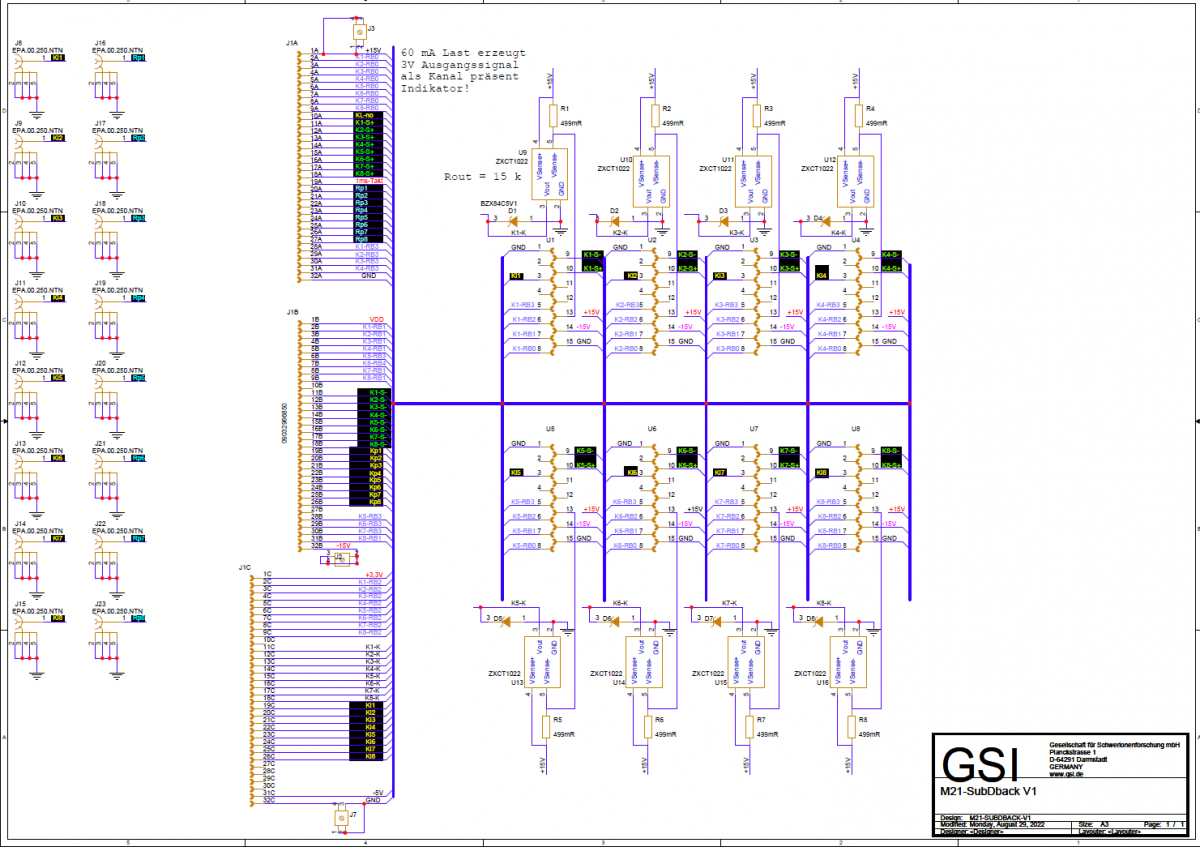

Schaltung SubDback Karte

Die Karte auf der Rückseite ist die Schnittstelle zu den Trafoanschlussleitungen. Hier können pro Modul acht Trafos angeschlossen werden. Versorgungsspannungen +/-15V und Groundanschluss wird hier ausgeführt. Es wird erkannt, ob ein Trafo am Anschluss angeschlossen ist oder nicht. Das entstandene Signal wird dem IO-Modul gestellt. In die +15V-Versorgung zum Trafo ist eine Serienwiderstand von 0,5 Ω eingefügt: Der Spannungsverlust von 30 mV wird vom Sensor detektiert und fest einhundertfach verstärkt. D.h. bei maximal Strom von 60 mA (Info MW) stehen 3V als Kanal präsent an.

festgestellte Schaltplanfehler

| Pos. | Kurz | Beschreibung | Fehlerbehandlung |

|---|---|---|---|

| 1 | Klemmpulseingang (TTL) an Klemmpulsausgang gekoppelt (CMOS) | An die Eingangsbuchse LEMO 00 wurde der falsche Signalname gekoppelt “Kl” x: somit werden ungewollt zwei Treiber mit unterschiedlichen Abgabepegeln aufeinander gelegt. Der richtige Signalname wäre “Kp” x, welches als TTL-Pegel auch über die VG-Federleiste in das Innere des Adapters gestellt wird! | Temporäre Lösung: Trennung der Leiterbahn der LEMO-Buchse zur benachtbarten VG und Einfügen der notwendigen Verbindung durch Drahtbrücke zum VG-Pin 19B.1) Längerfristig: Fehlerkorrektur und Platine korrigiert als “V2” ordern! |

| 2 | 1 Ω Messwiderstand liefert nur 35 mV | Der Sensor generiert aus dem Stromfluss des eingesteckten Trafos 2V. Das liegt harscharf auf High-Level “H” des LVTTL: Das Signal ist zu klein, um als “H” erkannt zu werden! | verdoppeln? |

1)

Die Selektormatrix funktioniert: über die Karte und ihre Jumper werden alle acht Trafos des ersten Modules mit dem an der ersten LEMObuchse eingespeißten Signal versorgt!