Wiki

User Tools

Sidebar

Table of Contents

☚ Messungen ★

L6: 1ms-Takt korrekt?

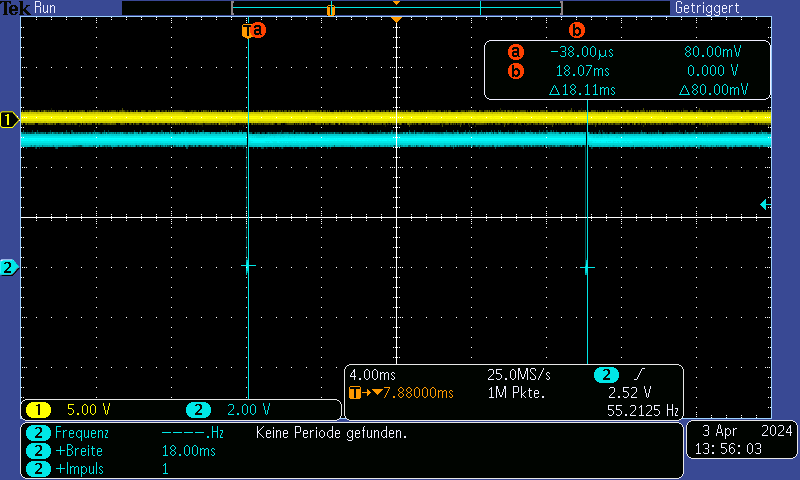

erstes Timing

1ms-Timing: Schaltung ☛

Das verschachtelte Doppeltiming wird durch zwei verschiedenen RC-Kombinationen bestimmt. Hier zunächst gesetzt waren:

T1 = 1,1 RG C5 = 19,5 ms#######mit C5 = 4,7µF, RG = 7,5 kΩ || 7,5 kΩ = 3,75 kΩ ! #######(R12/13)

T2 = 1,4 RG C2 = 1,00 ms#######mit C2 = 100 nF, RG = 7,5 kΩ || 150 kΩ = 7,143 kΩ ! #######(R10/11)

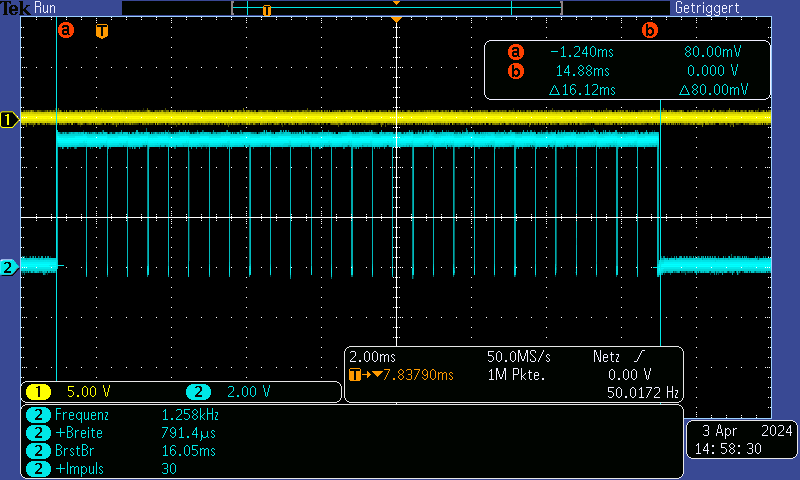

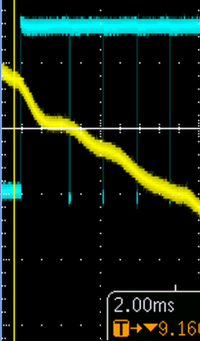

T1 = (18 ms) / 16,03ms#########⇒ C5-Ist = 3,886 µF (-20,9 %)

T2 = 791,4 µs#################⇒ C2-Ist = 79 nF (-21 %)

| Trotz 10%-Toleranzangabe weichen die Kapazitäten ab und müssen daher noch entsprechend korrigiert werden. Das geschieht am Besten durch rechnerisches Bestimmung der echten Cs gemäß Formel und Adaption durch Anpassung der Widerstände, die genauer festlegbar sind! |

Aus den Erstbestückungen ergibt sich rechnerisch, dass das C für das 19,5 ms-Intervall nicht die nominellen 4,7 µF hat sondern 3,886 µF. Für die gewünschte Ziellänge ergibt sich dann:

Korrigiertes Timing

T1 = 19,5 ms = 1,1 * RG * 3,886 µF#########⇒ RG = 4,615 kΩ (7,5 kΩ. || 12 kΩ)

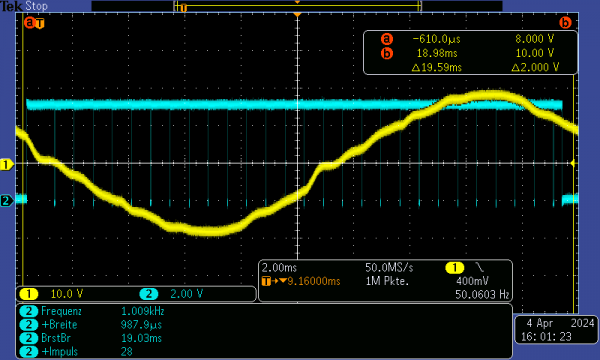

Für den das UNILAC-Timing als negativem Sinus ließt man ab, dass die Triggerung des 20ms-Intervalles bei einer Spannung von +8V geschieht, also etwas zu früh. Der Phasenwinkel dafür ergibt sich aus 8V = - 18 V sin(α) ⇒ α = - 26,4° (< 5min auf 1h). Das lässt sich am Komperator noch tunen!

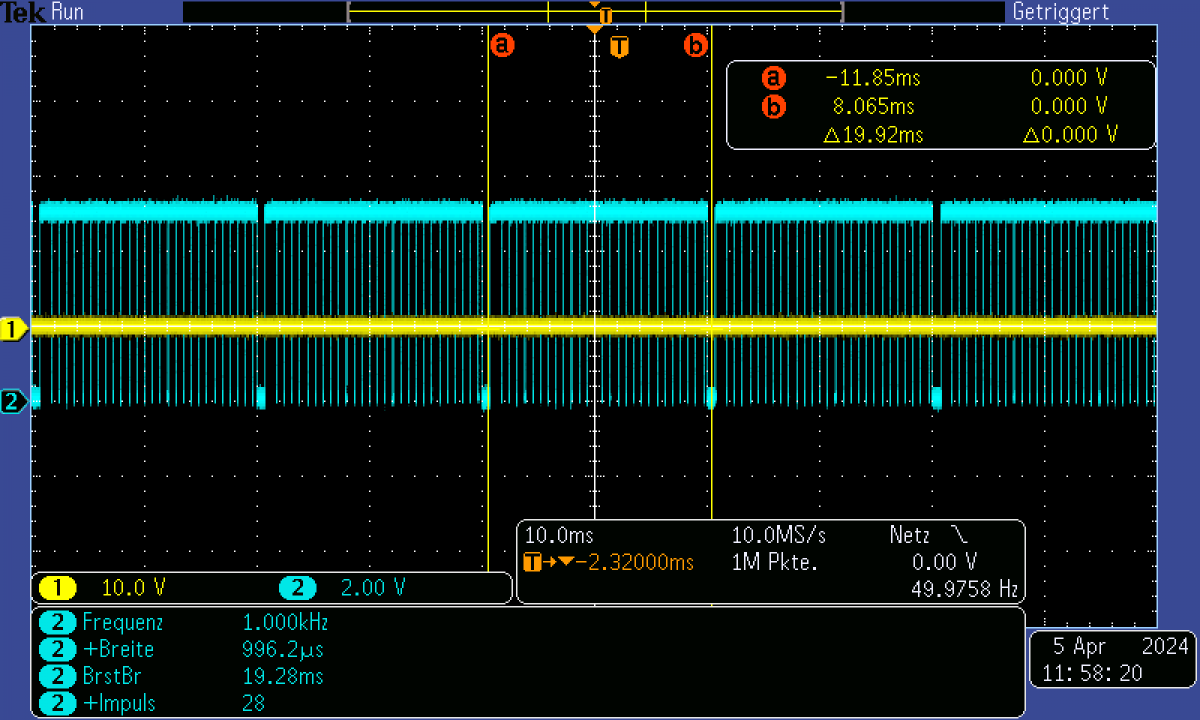

Mit den hier eingestellten RC-Kombinationen erhält man aus der AC-Phase des Steckernetzteiles getriggerte 19,5 µs Zeitintervalle. Darin sind dann dann die Millisekundenintervalle generiert, die die Anzeige benötigt. Warum sind das nun 28 Pulse und nicht nur die 20 anvisierten?

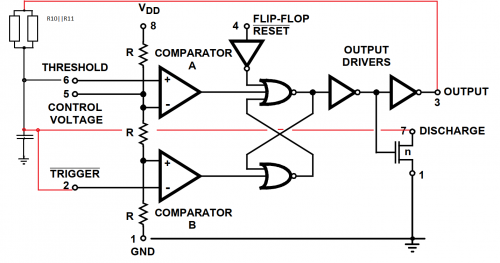

Man ließt ab, dass der erste 1ms-Takt genau diese Länge hat, aber das Zweite und die Folgenden dann nur noch 666 µs, also 2/3 s Länge haben. Da die Folgetakte also kürzer sind gibt es eben 28 statt 20 Pulse! Der erste Puls beginnt, wenn das Low der Vorstufe als /RESET der Zweiten durch das High des 20ms-Taktes ersetzt und der astabile Vibrator freigegeben wird: Die Spannung am zeitbestimmenden Kondensator startet dann bei 0 V und steigt bis zu Erreichen von 2/3 der Betriebsspannung (+5V) an, das NAND-Flipflop wird rückgesetzt:

1.) Wird dann der Threshold überschritten, dann werden das NAND-Flipflop und der Ausgang nach Treibern deaktiviert. Der Dischargetransistor schaltet den Eingangsknoten gegen Ground durch, die Kapazität C wird entladen, wobei der Entladeprozess kurz ist und nur durch den Serienwiderstand der Kapazität limitiert wird.

2.) Wird während des Entladens der Triggerlevel unterschritten so wird das Flipflop erneut gesetzt, der Transistor sperrt und der Kondensator wird wieder geladen. Nun ist diese Triggerschwelle aber nicht 0V sondern 1/3 der Betriebsspannung, sodass der nächste Ladezeitraum kürzer ist. Daraus resultieren die nachfolgend kürzeren Pulse!

Wenn also die meisten Pulse mit 666 µs nur 2/3 der Solllänge haben, dann muss folglich das Timingintervall um den Faktor 3/2 = 1,5 verlängert werden durch Wahl einer geeigneten Widerstandkombination!

☚ Messungen ★