☚ Schaltungen ★

| hinten >>>>>>>>> vorne | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||

| Schaltungen: | | | | | Front | Selektor | Q+D | Signaltransfer über alles |

|

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | X | |||

| Layouts: | | | | | Front | Selected | Q+D | ||

| SubDback-V2 | BackExtend-V2 | MDR-IO-V2 | DisplayContr-V2 | X | X | MDR-IO-V2 | |||

### Bestellt und in Herstellung (Leiterkarte) ### Ersetzt!

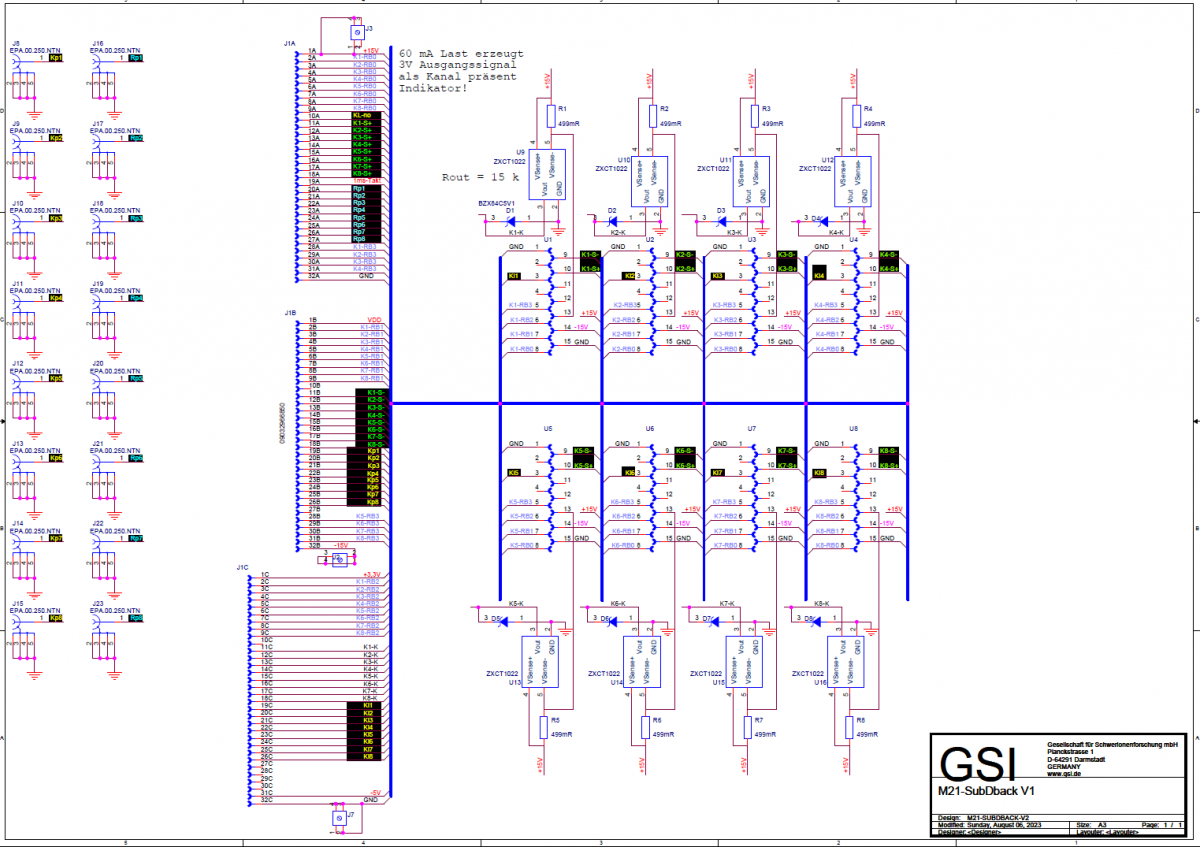

Schaltung SubDback Karte V2

Die Karte auf der Rückseite ist die Schnittstelle zu den Trafoanschlussleitungen. Hier können pro Modul acht Trafos angeschlossen werden. Versorgungsspannungen +/-15V und Groundanschluss wird hier ausgeführt. Es wird erkannt, ob ein Trafo am Anschluss angeschlossen ist oder nicht. Das entstandene Signal wird dem IO-Modul gestellt. In die +15V-Versorgung zum Trafo ist eine Serienwiderstand von 0,5 Ω eingefügt: Der Spannungsverlust von 30 mV wird vom Sensor detektiert und fest einhundertfach verstärkt. D.h. bei maximal Strom von 60 mA (Info MW) stehen 3V als Kanal präsent an.

Die an den LEMO-Buchsen eingehenden Pulse sind TTL-Pulse 50 Ω getrieben. Hier in“V2” wurden nun die richtigen Signalnamen “Kp” zugeordnet: damit ist im neuen Layout die Trennung von eingehenden TTL-Pegeln und ausgehenden CMOS-Pegeln (Trafos) gegeben! Das war in “V1” leider falsch gemacht worden, sodass Eingangs- und Ausgangspegel zusammen geführt wurden.

Festgestellte Layoutfehler

| Pos. | Fehler | Lösung |

|---|---|---|

| 1. | Signal Kp4 Klemmpulseingangs-LEMO-Buchse J11 ist nicht an VG22b angeschlossen! Die Verbindung im Schaltplan dort ist kaum erkennbar nicht bis an den VG-Pin geführt! | Drahtverbindung |

| 2. |