Wiki

User Tools

Sidebar

Signaltransfer

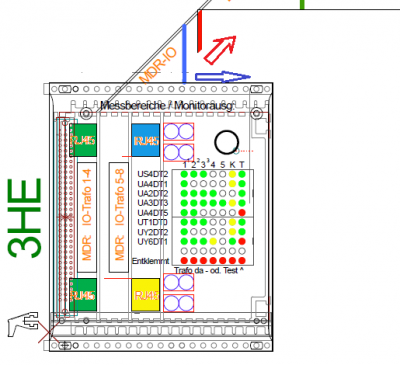

m Folgenden wird der Signalverlauf über die 96pol. VG-Leisten von hinten nach vorne projektiert. Das ist die Basis für die Schaltpläne der einzelnen Boards:

Generell stehen blase Farben für ungepufferte Signale (z.B. TTL) und starke Farben für gepufferte bzw. Pegelgewandelte Signal (z.B. CMOS an Trafo). Geplant sind Achtkanalmodule: daher steht “Kx-”… für den Kanal Nr. “x” und dann:

Tabelle VG Durchgang

Es gibt VG-Leisten längs im Crate von hinten nach vorne und VGs quer ab vom “MDR-IO” ineinander gesteckte Seiten-VGs. Die Pinbelegung an der Quer-VG darf, muss aber nicht die gleiche Belegung haben wie die Längs-VGs!

Leider gibt es einen Übergangsfehler zwischen MDR-IO und DisplayContr: an der VG-Pinnr. in ## markiert: Der ausgewählte Klemmpuls “Kl” wird mit 15V CMOS-Pegel zur Anzeige gebracht. Das ist zuviel für die LVTLL-Pegel der CPLDs. Es hätten die Klemmpulse “Klt” sein sollen! Die müssen nun auf neuem Displayboard heruntergeteilt werden.

| VG1 | SubDback | VG2 | Backextend | VG3 | MDR-IO | VG4 | DisplCont | Flachbd. | Front | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Pin | Signal | Pin | Pin | < hinten | vorne ^ | Seite> | Pin | ||||||

| 1 | 1a | +15V | 1a | +15V | 1a | +15V | \ X / | +15V | 1a | +15V | 1: | r1 | |

| 1b | +5V | 1b | +5V | 1b | +5V | \ X / | +5V | 1b | +5V | 2: | Rw1 | ||

| 1c | +3,3V | 1c | +3,3V | 1c | +3,3V | \ X / | +3,3V | 1c | +3,3V | 3: | r2 | ||

| 2 | 2a | K1-RB0 | 2a | K1-RB0 | 2a | K1-RB0 | \ K1-B0 / | K1-B0 | 2a | K1-B0 | 4: | Rw2 | |

| 2b | K1-RB1 | 2b | K1-RB1 | 2b | K1-RB1 | \ K1-B1 / | K1-B1 | 2b | K1-B1 | 5: | r3 | ||

| 2c | K1-RB2 | 2c | K1-RB2 | 2c | K1-RB2 | \ K1-B2 / | K1-B2 | 2c | K1-B2 | 6: | Rw3 | ||

| 3 | 3a | K2-RB0 | 3a | K2-RB0 | 3a | K2-RB0 | \ K2-B0 / | K2-B0 | 3a | K2-B0 | 7: | r4 | |

| 3b | K2-RB1 | 3b | K2-RB1 | 3b | K2-RB1 | \ K2-B1 / | K2-B1 | 3b | K2-B1 | 8: | Rw4 | ||

| 3c | K2-RB2 | 3c | K2-RB2 | 3c | K2-RB2 | \ K2-B2 / | K2-B2 | 3c | K2-B2 | 9: | r5 | ||

| 4 | 4a | K3-RB0 | 4a | K3-RB0 | 4a | K3-RB0 | \ K3-B0 / | K3-B0 | 4a | K3-B0 | 10: | Rw5 | |

| 4b | K3-RB1 | 4b | K3-RB1 | 4b | K3-RB1 | \ K3-B1 / | K3-B1 | 4b | K3-B1 | 11: | r6 | ||

| 4c | K3-RB2 | 4c | K3-RB2 | 4c | K3-RB2 | \ K3-B2 / | K3-B2 | 4c | K3-B2 | 12: | Rw6 | ||

| 5 | 5a | K4-RB0 | 5a | K4-RB0 | 5a | K4-RB0 | \ K4-B0 / | K4-B0 | 5a | K4-B0 | 13: | r7 | |

| 5b | K4-RB1 | 5b | K4-RB1 | 5b | K4-RB1 | \ K4-B1 / | K4-B1 | 5b | K4-B1 | 14: | Rw7 | ||

| 5c | K4-RB2 | 5c | K4-RB2 | 5c | K4-RB2 | \ K4-B2 / | K4-B2 | 5c | K4-B2 | 15: | r8 | ||

| 6 | 6a | K5-RB0 | 6a | K5-RB0 | 6a | K5-RB0 | \ K5-B0 / | K5-B0 | 6a | K5-B0 | 16: | - | |

| 6b | K5-RB1 | 6b | K5-RB1 | 6b | K5-RB1 | \ K5-B1 / | K5-B1 | 6b | K5-B1 | 17: | r9: | ||

| 6c | K5-RB2 | 6c | K5-RB2 | 6c | K5-RB2 | \ K5-B2 / | K5-Ri2 | 6c | K5-Ri2 | 18: | - | ||

| 7 | 7a | K6-RB0 | 7a | K6-RB0 | 7a | K6-RB0 | \ K6-B0 / | K6-B0 | 7a | K6-B0 | 19: | r10 | |

| 7b | K6-RB1 | 7b | K6-RB1 | 7b | K6-RB1 | \ K6-B1 / | K6-B1 | 7b | K6-B1 | 20: | - | ||

| 7c | K6-RB2 | 7c | K6-RB2 | 7c | K6-RB2 | \ K6-B2 / | K6-Ri2 | 7c | K6-B2 | 21: | g1 | ||

| 8 | 8a | K7-RB0 | 8a | K7-RB0 | 8a | K7-RB0 | \ K7-B0 / | K7-B0 | 8a | K7-B0 | 22: | - | |

| 8b | K7-RB1 | 8b | K7-RB1 | 8b | K7-RB1 | \ K7-B1 / | K7-B1 | 8b | K7-B1 | 23: | g2 | ||

| 8c | K7-RB2 | 8c | K7-RB2 | 8c | K7-RB2 | \ K7-B2 / | K7-B2 | 8c | K7-B2 | 24: | - | ||

| 9 | 9a | K8-RB0 | 9a | K8-RB0 | 9a | K8-RB0 | \ K8-B0 / | K8-B0 | 9a | K8-B0 | 25: | g3 | |

| 9b | K8-RB1 | 9b | K8-RB1 | 9b | K8-RB1 | \ K8-B1 / | K8-B1 | 9b | K8-B1 | 26: | - | ||

| 9c | K8-RB2 | 9c | K8-RB2 | 9c | K8-RB2 | \ K8-B2 / | K8-RB2 | 9c | K8-B2 | 27: | g4 | ||

| 10 | 10a | KL-no | 10a | KL-no | 10a | KL-no | X | < K5-RB0 | 10a | X | 28: | - | |

| 10b | 10b | 10b | X | < K5-RB1 | 10b | X | 29: | g5 | |||||

| 10c | 10c | 10c | X | < K5-RB2 | 10c | X | 30: | VDD(+5V) | |||||

| VG1 | SubDback | VG2 | Backextend | VG3 | MDR-IO | VG4 | DisplCont | Flachbd. | Front | ||||

| Pin | Signal | Pin | Pin | < hinten | vorne ^ | Seite> | Pin | ||||||

| 11 | 11a | K1-S+ | 11a | K1-S+ | 11a | K1-S+ | \ K1-NW+ / | < K6-RB0 | 11a | X | 31: | g6 | |

| 11b | K1-S- | 11b | K1-S- | 11b | K1-S- | \ K1-NW- / | < K6-RB1 | 11b | X | 32: | Ph1 | ||

| 11c | K1-K | 11c | K1-K | 11c | K1-K | \ X / ↓ | < K6-RB2 | 11c | X | 33: | g7 | ||

| 12 | 12a | K2-S+ | 12a | K2-S+ | 12a | K2-S+ | \ K2-NW+ / | < K7-RB0 | 12a | X | 34: | Ph2 | |

| 12b | K2-S- | 12b | K2-S- | 12b | K2-S- | \ K2-NW- / | < K7-RB1 | 12b | X | 35: | g8 | ||

| 12c | K2-K | 12c | K2-K | 12c | K2-K | \ X / ↓ | < K7-RB2 | 12c | X | 36: | S2 | ||

| 13 | 13a | K3-S+ | 13a | K3-S+ | 13a | K3-S+ | \ K2-NW+ / | < K8-RB0 | 13a | X | 37: | g9 | |

| 13b | K3-S- | 13b | K3-S- | 13b | K3-S- | \ K2-NW- / | < R8-RB1 | 13b | X | GND | GND | ||

| 13c | K3-K | 13c | K3-K | 13c | K3-K | \ X / ↓ | < K8-RB2 | 13c | X | 39: | g10 | ||

| 14 | 14a | K4-S+ | 14a | K4-S+ | 14a | K4-S+ | \ K2-NW+ / | K1-M > | 14a | K1-M | 40: | GND | |

| 14b | K4-S- | 14b | K4-S- | 14b | K4-S- | \ K2-NW- / | K2-M > | 14b | K2-M | ||||

| 14c | K4-K | 14c | K4-K | 14c | K4-K | \ X / ↓ | K4-M > | 14c | K4-M | ||||

| 15 | 15a | K5-S+ | 15a | K5-S+ | 15a | K5-S+ | \ K2-NW+ / | K1-K | 15a | K1-K | |||

| 15b | K5-S- | 15b | K5-S- | 15b | K5-S- | \ K2-NW- / | K5-K | 15b | K5-K | ||||

| 15c | K5-K | 15c | K5-K | 15c | K5-K | \ X / ↓ | K5-M > | 15c | K5-M | ||||

| 16 | 16a | K6-S+ | 16a | K6-S+ | 16a | K6-S+ | \ K2-NW+ / | K2-K | 16a | K2-K | |||

| 16b | K6-S- | 16b | K6-S- | 16b | K6-S- | \ K2-NW- / | K6-K | 16b | K6-K | ||||

| 16c | K6-K | 16c | K6-K | 16c | K6-K | \ X / ↓ | K6-M > | 16c | K6-M | ||||

| 17 | 17a | K7-S+ | 17a | K7-S+ | 17a | K7-S+ | \ K2-NW+ / | K3-K | 17a | K3-K | |||

| 17b | K7-S- | 17b | K7-S- | 17b | K7-S- | \ K2-NW- / | K7-K | 17b | K7-K | ||||

| 17c | K7-K | 17c | K7-K | 17c | K7-K | \ X / ↓ | K7-M > | 17c | K7-M | ||||

| 18 | 18a | K8-S+ | 18a | K8-S+ | 18a | K8-S+ | \ K2-NW+ / | K4-K | 18a | K4-K | |||

| 18b | K8-S- | 18b | K8-S- | 18b | K8-S- | \ K2-NW- / | K8-K | 18b | K8-K | ||||

| 18c | K8-K | 18c | K8-K | 18c | K8-K | \ X / ↓ | K8-M > | 18c | K8-M | ||||

| 19 | 19a | 1ms-Takt | 19a | 1ms-Takt | 19a | 1ms-Takt | X | 1ms-Takt | 19a | 1ms-Takt | |||

| 19b | Kp1 | 19b | Kp1 | 19b | Kp1 | X | Kp1 | 19b | Kp1 | ||||

| 19c | Kl1 < ' | 19c | Kl1 < ' | 19c | Kl1 < ' | X | Kl1 < ' | 19c | Kl1 < ' | ||||

| 20 | 20a | Rp1 | 20a | Rp1 | 20a | Rp1 | \ K1-Rp- / | Rp1 | 20a | Rp1 | |||

| 20b | Kp2 | 20b | Kp2 | 20b | Kp2 | X | Kp2 | 20b | Kp2 | ||||

| 20c | Kl2 < ' | 20c | Kl2 < ' | 20c | Kl2 < ' | X | Kl2 < ' | 20c | Kl2 < ' | ||||

| VG1 | SubDback | VG2 | Backextend | VG3 | MDR-IO | VG4 | DisplCont | Flachbd. | Front | ||||

| Pin | Signal | Pin | Pin | < hinten | vorne ^ | Seite> | Pin | ||||||

| 21 | 21a | Rp2 | 21a | Rp2 | 21a | Rp2 | \ K2-Rp- / | Rp2 | 21a | Rp2 | |||

| 21b | Kp3 | 21b | Kp3 | 21b | Kp3 | X | Kp3 | 21b | Kp3 | ||||

| 21c | Kl3 < ' | 21c | Kl3 < ' | 21c | Kl3 < ' | X | Kl3 < ' | 21c | Kl3 < ' | ||||

| 22 | 22a | Rp3 | 22a | Rp3 | 22a | Rp3 | \ K3-Rp- / | Rp3 | 22a | Rp3 | |||

| 22b | Kp4 | 22b | Kp4 | 22b | Kp4 | X | Kp4 | 22b | Kp4 | ||||

| 22c | Kl4 < ' | 22c | Kl4 < ' | 22c | Kl4 < ' | X | Kl4 < ' | 22c | Kl4 < ' | ||||

| 23 | 23a | Rp4 | 23a | Rp4 | 23a | Rp4 | \ K4-Rp- / | Rp4 | 23a | Rp4 | |||

| 23b | Kp5 | 23b | Kp5 | 23b | Kp5 | X | Kp5 | 23b | Kp5 | ||||

| 23c | Kl5 < ' | 23c | Kl5 < ' | 23c | Kl5 < ' | X | Kl5 < ' | 23c | Kl5 < ' | ||||

| 24 | 24a | Rp5 | 24a | Rp5 | 24a | Rp5 | \ K5-Rp- / | Rp5 | 24a | Rp5 | |||

| 24b | Kp6 | 24b | Kp6 | 24b | Kp6 | X | Kp6 | 24b | Kp6 | ||||

| 24c | Kl6 < ' | 24c | Kl6 < ' | 24c | Kl6 < ' | X | Kl6 < ' | 24c | Kl6 < ' | ||||

| 25 | 25a | Rp6 | 25a | Rp6 | 25a | Rp6 | \ K6-Rp- / | Rp6 | 25a | Rp6 | |||

| 25b | Kp7 | 25b | Kp7 | 25b | Kp7 | X | Kp7 | 25b | Kp7 | ||||

| 25c | Kl7 < | 25c | Kl7 < ' | 25c | Kl7 < ' | X | Kl7 < ' | 25c | Kl7 < ' | ||||

| 26 | 26a | Rp7 | 26a | Rp7 | 26a | Rp7 | \ K7-Rp- / | Rp7 | 26a | Rp7 | |||

| 26b | Kp8 | 26b | Kp8 | 26b | Kp8 | X | Kp8 | 26b | Kp8 | ||||

| 26c | Kl8 < | 26c | Kl8 < ' | 26c | Kl8 < ' | X | Kl8 < ' | 26c | Kl8 < ' | ||||

| 27 | 27a | Rp8 | 27a | Rp8 | 27a | Rp8 | \ K8-Rp- / | Rp8 | 27a | Rp8 | |||

| 27b | 27b | 27b | X | K3-M > | 27b | K3-M > | |||||||

| 27c | 27c | 27c | X | < K5-RB3 | 27c | X | |||||||

| 28 | 28a | K1-RB3 | 28a | K1-RB3 | 28a | K1-RB3 | \ K1-B3 / | K1-B3 | 28a | K1-B3 | |||

| 28b | K5-RB3 | 28b | K5-RB3 | 28b | K5-RB3 | \ K5-B3 / | K5-B3 | 28b | K5-B3 | ||||

| 28c | 28c | 28c | X | < K6-RB3 | 28c | X | |||||||

| 29 | 29a | K2-RB3 | 29a | K2-RB3 | 29a | K2-RB3 | \ K2-B3 / | K2-B3 | 29a | K2-B3 | |||

| 29b | K6-RB3 | 29b | K6-RB3 | 29b | K6-RB3 | \ K6-B3 / | K6-B3 | 29b | K6-B3 | ||||

| 29c | 29c | 29c | X | < K7-RB3 | 29c | X | |||||||

| 30 | 30a | K3-RB3 | 30a | K3-RB3 | 30a | K3-RB3 | \ K3-B3 / | K3-B3 | 30a | K3-B3 | |||

| 30b | K7-RB3 | 30b | K7-RB3 | 30b | K7-RB3 | \ K7-B3 / | K7-B3 | 30b | K7-B3 | ||||

| 30c | 30c | 30c | X | < K8-RB3 | 30c | X | |||||||

| VG1 | SubDback | VG2 | Backextend | VG3 | MDR-IO | VG4 | DisplCont | Flachbd. | Front | ||||

| Pin | Signal | Pin | Pin | < hinten | vorne ^ | Seite> | Pin | ||||||

| 31 | 31a | K4-RB3 | 31a | K4-RB3 | 31a | K4-RB3 | \ K4-B3 / | K4-B3 | 31a | K4-B3 | |||

| 31b | K8-RB3 | 31b | K8-RB3 | 31b | K8-RB3 | \ K8-B3 / | K8-B3 | 31b | K8-B3 | ||||

| 31c | -5V | 31c | -5V | 31c | -5V | \ X / | -5V | 31c | -5V | ||||

| 32 | 32a | GND | 32a | GND | 32a | GND | ┬ | GND | 32a | GND | |||

| 32b | -15V | 32b | -15V | 32b | -15V | \ X / | -15V | 32b | -15V | ||||

| 32c | GND | 32c | GND | 32c | GND | GND | 32c | GND | |||||

| KL-no | KL-no | ||||||||||||