Wiki

User Tools

Sidebar

ds:software:hdl

This is an old revision of the document!

Table of Contents

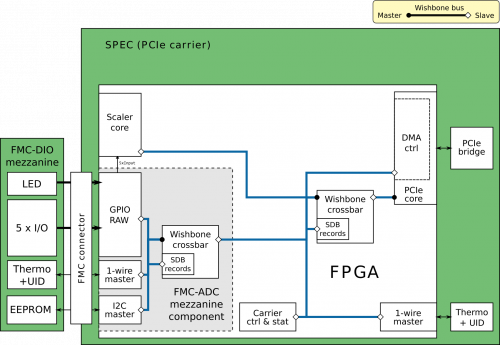

SPEC Scaler

| BusPath | VendorID | Product | BaseAddress(Hex) | Description |

|---|---|---|---|---|

| 1 | 000000000000ce42 | ff07fc47 | 0x1000 | WR-Periph-Syscon |

| 2 | 000000000000ce42 | e2d13d04 | 0x2000 | WR-Periph-UART |

| 3 | 000000000000ce42 | 779c5443 | 0x3000 | WB-OneWire-Master |

| 4 | 0000000000000651 | eef0b198 | 0x2000 | WB4-Bridge-GSI |

| 4.1 | 000000000000ce42 | 123c5443 | 0x3000 | WB-I2C-Master |

| 4.2 | 000000000000ce42 | 779c5443 | 0x3100 | WB-OneWire-Master |

| 4.3 | 000000000000a8df | 441c5145 | 0x3200 | WB-GPIO-RAW |

| 5 | 000000000000a8df | 441c5146 | 0x5000 | WB-SCALER |

Final design

Initialization

- configure inputs

- direction (WB-GPIO-RAW⇒DDR)

- termination (WB-GPIO-RAW⇒TR)

- setup input map registers

- WB-SCALER⇒CounterMap

- WB-SCALER⇒LatchMap

- WB-SCALER⇒StartStopMap

- reset all counters by writing 1 to WB-SCALER⇒SC - empty/reset bit

- enable scaler (optional) by writing 1 to WB-SCALER⇒SC - running/start bit

Data readout

- Check status register (empty bit) if new data is available

- Latch new data into circular buffer (WB-SCALER⇒OCounter) by writing load_fifo bit

- Read OCounter register four times.

FMC

- repository: LOBI IP Cores

- repository: FMC HDL

FMC Dio 5ch TTL

TODO

| BusPath | VendorID | Product | BaseAddress(Hex) | Description |

|---|---|---|---|---|

| 1 | 000000000000???? | ???????? | 0x0000 | WB4-Bridge-GSI |

| 2 | 000000000000???? | ???????? | 0x1000 | WR-Periph-1Wire |

| 3 | 000000000000???? | ???????? | 0x1100 | WB-I2C-Master |

| 4 | 000000000000???? | ???????? | 0x1200 | WB-GPIO-RAW |

WR Cores

WB Scaler

- master_mode ⇒ PIPELINED

- master_granularity ⇒ WORD

Register map

| Register | Address | Default Value | Description |

|---|---|---|---|

| SC | 0b000 | 0x00000001 | Status and control |

| CounterMap | 0b001 | 0x08040201 | |

| LatchMap | 0b010 | 0x00000010 | Bit 8 wired to software latch |

| StartStopMap | 0b011 | 0x00000080 | Bit 8 wired to software start/stop |

| CCounter | 0b100 | 0x00000000 | |

| LCounter | 0b101 | 0x00000000 | |

| OCounter | 0b110 | 0x00000000 | |

| FCounter | 0b111 | 0xFFFFFFFF |

Register description

SC (0b000)

| Bits | hex | Name | R/W | Description |

|---|---|---|---|---|

| 0 | (0x01) | empty/reset | rw | |

| 1 | full | r | ||

| 2 | threshold | r | ||

| 3 | (0x08) | running/start | rw | |

| 4 | (0x10) | stop | w | |

| 5 | (0x20) | load_current | w | |

| 6 | (0x40) | load_fifo | w | |

| 7 | (0x80) | software_latch | w | |

| 11 - 8 | counter_ovf | r |

CounterMap (0b001)

| Bits | Name | R/W | Description |

|---|---|---|---|

| 7 - 0 | counter[0] | rw | |

| 15 - 8 | counter[1] | rw | |

| 23 - 16 | counter[2] | rw | |

| 31 - 24 | counter[3] | rw |

WB GPIO Raw

- g_master_mode ⇒ CLASSIC

- g_master_granularity ⇒ WORD

Register map

| Register | Address | Default Value | Description |

|---|---|---|---|

| CODR | 0b000 | 0x00000000 | |

| SODR | 0b001 | 0x00000000 | |

| DDR | 0b010 | 0x00000000 | |

| PSR | 0b011 | 0x00000000 | |

| TR | 0b100 | 0x00000000 | |

| AFR | 0b101 | 0x00000000 |

ds/software/hdl.1455538096.txt.gz · Last modified: 2016/02/15 13:08 by pmiedzik