Table of Contents

☚ Messungen ★

Labormessung "L15"-M#5-Timing

| Monitormessung ausstehend! |

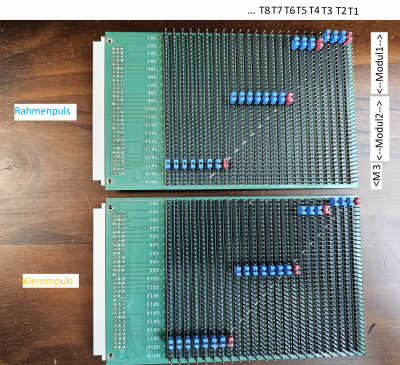

Klemm- und Rahmenpuls an MDR-IO-V2-Var.1/2

Über die Auswahlmatrix der “Selector”-Karte werden rückwärtig angeschlossenen Timingsignal auf das jeweilige frontseitige Modul geroutet: Die acht vom Modul angesteuerten Trafos können dann beliebig in die gewählten Timingzonen “eingehängt” werden. Jeweils vier dieser Klemm- und Rahmenpulse werden zur DAQ-Erfassung ebenfalls auf die Netzwerkbuchsen ihren differentiellen Kanälen gestellt. Der Unterschied zu den zuvor getesten analogen Trafosignalen (L4 ☛), die wirklich jeden Wert in den erlaubten +/- 1V-Grenzen einnehmen können ist, dass die eingehenden Signale nicht differentiell, sondern GND-bezogen single ended einlaufen und eigentlich nur digitale Zustände “Puls da/nicht da” haben!.

Rahmenpulse K1-4

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Zweig1) zum Trafo: | von hinten | > | vor 50Ω-Abschluss | > | am Selektor gewählt | > | VOR 1V-Teilung | > | Eingang Buffer | > | Differentiell@50Ω | > | zur DAQ |

| Check: | K1..4 ✔ K5-8 ? | K1..4 ✔ K5-8 ? | 1:1 per Jumper an J8 statt Selektor | K1..4 ✔ K5-8 ? | K1..4 ✔ K5-8 ? | K1..4 ✔ K5-8 ? | K1..4 ✔ K5-8 ? |

||||||

| Wo? | SubDback Plan ☛ | BackExtend Plan ☛ | SelektorVG-c Plan ☛ | MDR-IO-V2 Blatt3 ☛ | MDR-IO-V2 Blatt3 ☛ | MDR-IO-V2 Blatt3 ☛ | MDR-IO-V2 Blatt3 ☛ |

||||||

| Name: | Rp[1..8] | Rp[1..8] | Rp-[a..h] | Rp-[a..h] / Rp[1-8] | R[1..4]2) | AB+/AB- | NW+/NW- | ||||||

| Pegel: | 5V-TTL>50Ω | 5V-TTL>50Ω | 5V-TTL>25kΩ ############## | 5V-TTL>25kΩ ############## | 1V3) ############## | +/- 1V | +/- 1V ############## |

||||||

Messungen Rahmenpuls

Klemmpulse (K1-4) an DAQ UND Trafo (K1..8)

Das Flachbandkabel für den Klemmpuls ist für Modul1 korrekt. Der Fehler KL4 im Schaltplan wurde mit Dätchen eliminiert! keinen Durchgang gibt! Für die Prüfung der Klemmpulssignale hier die Klemmpulskette:

| 1. | 2. | 3. | 4. | 5. | 6. | 7. | 8. | 9. | 10. | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Zweig4) zum Trafo : | von hinten | > | vor 50Ω-Abschluss | > | am Selektor gewählt | > | VOR 1V-Teilung | > | Eingang Buffer | > | invertiert | > | abgekoppelt | > | ex.Timg. frei synth. | > | ab Pegelwandler | Zum Trafo | |

| Check: | ✔ | 1:1 per Jumper an J9 statt Selektor | ✘ | ✔ | ——————→ | ✔ | ✔ | ✔ | K1-4 ✔ K5-8 ✔ | K1-4 ✔ K5-8 ✔ |

|||||||||

| Wo? | SubDback Plan ☛ | BackExtend Plan ☛ | SelektorVG-c Plan ☛ | MDR-IO-V2 Blatt3 ☛ | MDR-IO-V2 Blatt3 ☛ | MDR-IO-V2 Blatt2☛ | MDR-IO-V2 Blatt2☛ | MDR-IO-V2 Blatt2☛ | MDR-IO-V2 Blatt1 | SubDback SubDback |

|||||||||

| Name: | Kl[1..8] | Kp[1..8] | Kp-[a..h] | Kp-[a..h] / Kp[1-8] | ——————→ | namenlos | Kabg.[1..8] | Klf[1..8] | Kl[1..8] | Kl[1..8] | |||||||||

| Pegel: | 5V-TTL>50Ω | 5V-TTL>50Ω | 5V-TTL>25kΩ | 5V-TTL>25kΩ |  | ——————→ | 5V | 5V ############## | 5V ############## | 12-15V CMOS | 12-15V CMOS |

||||||||

| Zweig zur DAQ | ↓ | Eingang Buffer | > | Differentiell@50Ω | > | zur DAQ | |||||||||||||

| Wo? | ↓ | MDR-IO-V2 | MDR-IO-V2 | MDR-IO-V2 | |||||||||||||||

| Name: | ↓ | K[1..4]5) | AB+/AB- | NW+/NW- | |||||||||||||||

| Pegel: | ↓ | ############## | 1V6) | ✔ | +/- 1V | ✔ | +/- 1V | ✔ | |||||||||||

| Zweig zum Display | zum DisplayContr. | Pins J3-p | |||||||||||||||||

| Wo? | DisplayContr-V2 | ||||||||||||||||||

| Name: | Kp[1..8] / Klt[1..8] | ||||||||||||||||||

| Pegel: | 5V ############## | ############## |

Messungen Klemmpuls

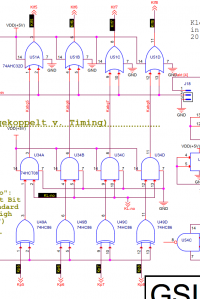

Hier werden die invertierten Klemmpulse erfasst. Dazu wird das Bit “Kl-no” am Pfostenbinder zum Displayboard mit 5V ab VG-Pin1b beschickt! Dieses Bit wird gewöhnlich von der DAQ gesetzt, die hier noch nicht angeschlossen ist.

Hinweis: Die relevante Logikgatter sind U49>U34>U51 auf der MDR-IO-V2 Variante U/L im rechten unteren Platineneck zu bestücken!

Klemmlogik für zweite Gruppe Trafos U49 > U34 > U51: | Klemmlogik für zweite Gruppe Trafos STATT auf Karte “MDR-IO-V2” Links/Unten nun Karte Rechts/Oben bestücken! |