Technical Information Manual

MOD. A200

H.V. CAENET VME CONTROLLER

16th April 1991

CAEN will repair or replace any product within the guarantee period if the guarantor declares that the product is defective due to workmanship or materials and has not been caused by mishandling, negligence on behalf of the user, accident or any abnormal conditions or operations.

CAEN reserves the right to change partially or entirely the contents of this manual at any time and without giving any notice.

## TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                    | page                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                       | 2                                                                             |

| <ol> <li>SYSTEM OVERVIEW</li> <li>SET PARAMETER VALUE sequence</li> <li>READ PARAMETER VALUE sequence</li> </ol>                                                                                                                                                                                                                                                                   | 3<br>3<br>4                                                                   |

| <ul> <li>2. VME CYCLES (referring to the SY 127 System) <ol> <li>SELECT TARGET</li> <li>WRITE DATA</li> <li>START READOUT</li> <li>READ VALUE(S)</li> </ol> </li> <li>2.5 DATA BUS LINES interpretation <ol> <li>SELECT TARGET</li> <li>WRITE DATA</li> </ol> </li> <li>3.1 SELECT TARGET <ol> <li>WRITE DATA</li> <li>START READOUT</li> <li>READ VALUE(S)</li> </ol> </li> </ul> | 5<br>6<br>8<br>10<br>12<br>12<br>14<br>15<br>15<br>15<br>15<br>16<br>17<br>18 |

| 4. RESET                                                                                                                                                                                                                                                                                                                                                                           | 20                                                                            |

| 5. READ VALIDITY of actions                                                                                                                                                                                                                                                                                                                                                        | 20                                                                            |

| 6. ERROR CODES                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                            |

| Components List and Location                                                                                                                                                                                                                                                                                                                                                       | Appendix A                                                                    |

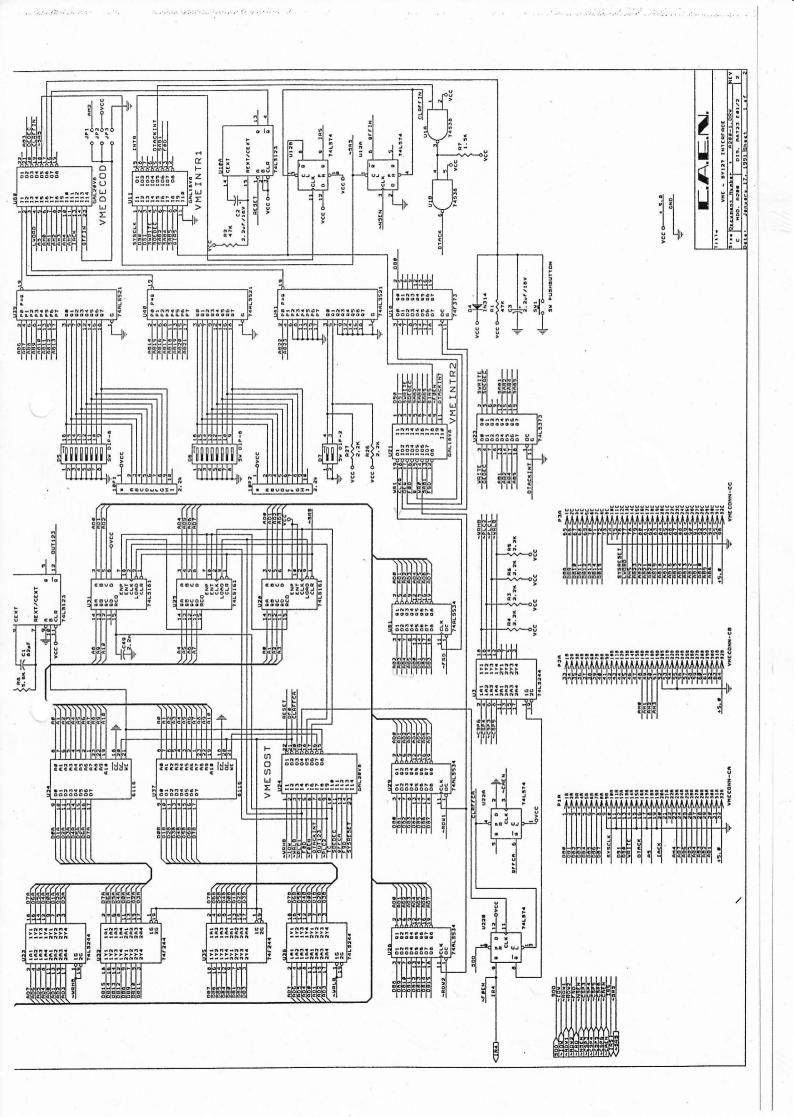

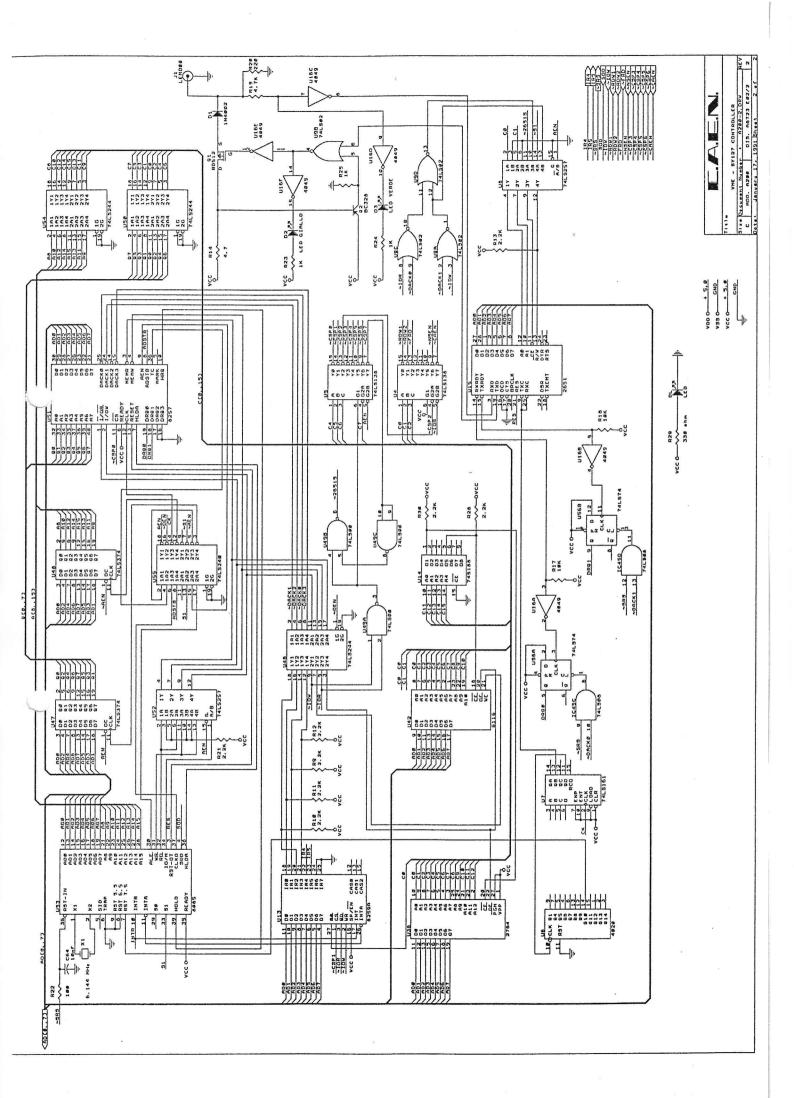

| Electrical Diagrams                                                                                                                                                                                                                                                                                                                                                                | Appendix B                                                                    |

## CAEN A200 VMIE INTIERFACE

## **INTRODUCTION**

# The model A200 is the VME Interface for the CAEN SY 127 and SY 227 High Voltage Systems.

It allows the user to carry out the full monitoring and control of a HV system from any computer connected to VME. In this way, for each application, a dedicated software can be developed using high-level languages.

Appropriate error codes are returned for any operation performed on the system.

Up to 100 crates daisy-chain connected, for a maximum of 4000 High Voltage channels, can be controlled by a single A200 unit. The module is one VME unit wide.

Information is exchanged between the A200 and the SY 127 OR SY 227 System via a HIGH VOLTAGE CAENET Serial link, which uses a 50  $\Omega$  coaxial cable as a physical medium.

## 1. SYSTEM OVERVIEW

Two basic kinds of actions can be thought of in connection with the monitoring and the control of a HV system, i.e. setting a parameter's value and reading it out.

Both actions can be expanded in a sequence of operations, where each operation is performed via Read and Write VME Cycles.

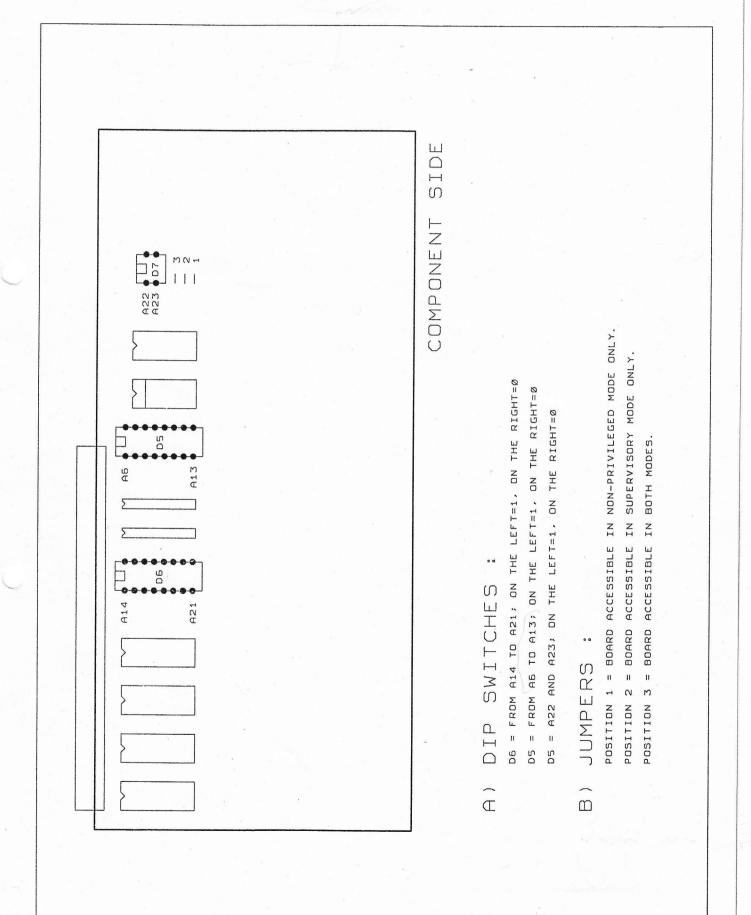

A200 is a D16, A16 and A24 Slave, that is, it supports transfers of 16 bits Data and can be addressed with 16 or 24 Address Lines. User can select the page in memory in which to place the module via dip-switches on A23-A6 Address Lines.

It is also possible to decide (jumper selection) if A200 belongs to user or to supervisor space or to both.

#### 1.1 SET PARAMETER VALUE sequence

This is expanded in:

SELECT TARGET READ ERROR FLAG WRITE DATA READ ERROR FLAG

a) SELECT TARGET is intended to specify which Channel, group of Channels, or block of HV parameters are the target of the subsequent WRITE DATA operation (which actually performs the setting of the parameter's value).

SELECT TARGET is needed only when a new target has to be specified, i.e. in case of consecutive actions performed on the same target (e.g. changing several parameters of the same HV Channel ) only one target selection is required at the beginning.

Possible targets are a single HV Channel (HV parameters which can be actually set through VME are detailed under the WRITE DATA specifications below ), a Group of Channels (same remark ), a set of global Crate Protection bits, and the set of parameters describing the status of the Streamer-tubes-conditioning process ( they are read-only parameters ).

It is worth noticing that only one Crate at a time can be acted upon (its number being given in the SELECT TARGET Data field).

b) WRITE DATA performs the setting of the parameter, whose new value is in the VME Data Bus (from DB0 to DB15).

Only a limited set of parameters ( detailed below ) can be set through VME for a single Channel, or in parallel for a group of Channels. For some parameters even (as for the Channel Status), only few specific bits can be modified.

c) READ ERROR FLAG can be performed at any time to find out the outcome of a previous operation.

A single negative word read out corresponds to an error condition (see (a) note 2.4).

Note: The use of READ ERROR FLAG is strongly recommended for one correct synchronisation through the user software end the VME interface.

## 1.2 READ PARAMETER VALUE sequence

This is expanded in:

SELECT TARGET READ ERROR FLAG START READOUT READ VALUE(S)

- a) **SELECT TARGET** has the same form, meaning and limitations as in the SET PARAMETER VALUE sequence.

- b) START READOUT is needed, in case of a READ sequence, in order to steer the readout on a specific subset of the vast parameters' set: thus, the readout of the (one or several) resulting parameter values can be performed most effectively with a Q-STOP read operation (see the READ VALUE) below, without any further subaddress specification.

- c) READ VALUE(S) reads out a block of data, one or more words depending on which target was specified in the SELECT TARGET and on the subset chosen in the previous START READOUT.

A single negative word read out corresponds to an error condition occurred during the previous operation (which had to be a START READOUT).

## 2. VME CYCLES (referring to the SY 127 system)

The necessary VME Cycles for every sequence are detailed. In the following, bits A23-A6 are ignored. Refer to the SY 127 System Manual for further information and for the meaning of the Channels' parameters.

### 2.1 SELECT TARGET

Select Target is performed by two Write Cycles: <u>Write</u> at Address 18, with bits 0-7 of Data Bus selecting the desired target and bits 8-15 specifying the number (between 0 and 99) of a Crate in the SY 127 System. Write at Address 14 mith bits 0.15 a D to D

Write at Address 1A, with bits 0-15 of Data Bus ignored.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1A:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation;

bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not accepted, in this case repeat the action performed; bits 1to 15 of Data Bus (DB1to DB15) are ignored.

Crate numbers 100 to 255 are reserved to the System. An invalid crate number at this stage is immediately reported as an error code -1.

The value of the lower byte of the Data Bus Lines is interpreted as follows:

- 0-39 gives the number of the Channel selected (40 Channels per Crate max.).

- 40-48 selects a block of parameters relative to the Streamer-tubes-conditioning process, specifically:

- 40 selects one of the values of the Voltages (V0-V15)

- 41 selects one of the values of the Currents (IO-I15)

- 42 selects one of the values of Time-High (TH0-TH15)

- 43 selects one of the values of Time-Low (TL0-TL15)

- 44 selects the Maximum Width Time of a conditioning step

- 45 selects the Ramp-up rate

- 46 selects the Ramp-down rate

- 47 selects the set of three possible commands:

- Start (BIT 0), Stop (BIT 1), Pause (BIT 2)

- 48 selects the Total Width Time of the conditioning process

Warning: these parameters can only be read out, and not written on. Any subsequent attempt to write on them via a WRITE DATA will result in an error code -48.

For targets 40-43, the Data Bus Lines in the Start-Readout operation (see below) selects which one of the corresponding 16 values has to be read.

50-57 selects a Global Absolute Group as follows:

- 50 Group ALL

- 51 Group A

- 52 Group B

- 53 Group C

- 54 Group D

- 55 Group E

- 56 Group F

- 57 Group G

60-67 selects a Global Relative Group as follows:

- 60 Group ALL

- 61 Group A

- 62 Group B

- 63 Group C

- 64 Group D

- 65 Group E

- 66 Group F

- 67 Group G

- 70

- selects the Protection bits

- 2.2 WRITE DATA

Write Data is performed by two Write Cycles: <u>Write</u> at Address IC, with bits 0-15 of Data Bus containing Data to be written.

<u>Write</u> at Address 1E, with bits 0-3 of Data Bus containing the subaddress which selects the parameter to write.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1E:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation;

bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not accepted, in this case repeat the action performed; bits 1to 15 of Data Bus (DB1to DB15) are ignored.

a) For a Single Channel Selection (Target = 0-39 in the Select Target operation) only subaddresses 0 to 8 are allowed.

Use of a subaddress > 8 will result in the error -5.

The meaning of the subaddresses is:

- 0 selects the setting of V0

- 1 selects the setting of V1

- 2 selects the setting of I0

- 3 selects the setting of I1

- 4 selects the setting of the Ramp-up rate

- 5 selects the setting of the Ramp-down rate

- 6 selects the setting of the Trip

- 7 selects the setting of the Status bits \* (see note over page)

- 8 selects the setting of the Channel to Group assignment bits \*\* (see note over page)

- b) For a Global Absolute Group Selection (Target = 50-57), only the subaddresses 0-7 of the above list are allowed (see note on page 21).

Use of subaddress 8 will result in the error -9. Use of a subaddress > 8 will result in the error -5.

c) For a Global Relative Group Selection (Target = 60-67), only the subaddresses 0-6 of the above list are allowed.

Use of subaddresses 7 and 8 will result in the error -11. Use of a subaddress > 8 will result in the error -5.

d) For a Protection Bits Selection (Target = 70) the subaddress is ignored, and only the first 4 bits of the data field are used\*\*\* (see note below). Any attempt to write a bit which is different from 0-3 will result in error -12.

#### **IMPORTANT:**

The setting of the Write Lines depends on the HV module on which one has to act as well as on the operation to be performed. Refer to Chapter 2.5 for details.

#### NOTES:

#### \*) Status Bits

The only Status bit which can be changed via VME is bit 0, the ON/OFF bit. If a 1 is written on bit 0, the Channel is turned ON, if a 0 is written, the Channel is turned OFF.

Any attempt to write on a Status bit different from bit 0 will result in error -4.

#### \*\*) Channel to Group assignment Bits

A mask on Data Bus Lines is used to describe which Groups a Channel will belong to (the Channel to Group assignment bits): bit 0 represents Group ALL, bit 1 Group A, and so on to bit 7 which represents Group G. If one of these bits is set to 1, the Channel will belong to the corresponding Group, if it is set to 0 the Channel will be discarded from that Group.

Care must be taken, before giving such a command, to read the current status, in order to find out which Groups a Channel belongs to (see note on page 21).

#### \*\*\*)Protection Bits

In changing the Protection Bits ( Target = 70 ), the subaddress is ignored, and only the first 4 bits of the data field are used.

If a bit is set to 1, the corresponding Protection is enabled, if it is set to 0, the Protection is disabled.

Care must be taken, when modifying the Protection Bits, to act only on the relevant ones, leaving the others unchanged.

The meaning of these 4 bits is:

bit 0 Power ON bit 1 Password enable bit 2 Keyboard enable bit 3 Clear Alarm

#### Note on the Alarm bit:

If during a READ operation this bit is set to 1, then an Alarm condition has taken place, which could be due to a Trip-off, an Over-voltage or an Under-voltage status of the channel. An alarm condition can be reset (Clear Alarm operation) writing a I on bit 3: then the bit should toggle to zero if it was set, or stay zero if no alarm condition was present. Warning: if, following a Clear Alarm operation, bit 3 is still set to 1, then the Alarm condition persists, and it is caused either by an Over-voltage or by an Under-voltage status of the HV channel.

### 2.3 START READOUT

Start Readout is performed by two Write Cycles:

Write at Address 18, with bits 0-7 of Data Bus ignored and bits 8-15 all set to 1.

Write at Address 1A, with bits 0-3 of Data Bus containing the subaddress which selects the parameter to read.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1A:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation;

bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not accepted, in this case repeat the action performed;

bits 1to 15 of Data Bus (DB1to DB15) are ignored..

a) For a Single Channel Selection (Target = 0-39) the subaddress meaning is:

- selects the readout of V0 0

- selects the readout of V1 1

- 2 selects the readout of I0

- 3 selects the readout of I1

- 4 selects the readout of the Ramp-up rate

- 5 selects the readout of the Ramp-down rate

- 6 selects the readout of the Trip setting

- 7 selects the readout of the Channel Status

- 8 selects the readout of the Channel to Group assignment bits

- 9 selects the readout of VMON

- 10 selects the readout of IMON

- 11 selects the readout of the Phase of the Streamer tubes conditioning process (see note \* below)

- 12 selects the readout of the Time of the Streamer-tubes-conditioning process (see note \* below)

- 13 selects the readout of the Channel Type

- 14 invalid

- 15 selects the readout of all the parameters in a block (see note \*\* below)

#### Notes:

\*) The Streamer-Tubes-Conditioning can only take place on channels belonging to Group A.

Thus the values read back with subaddresses 11 and 12, when working on a channel belonging to a Group different from Group A, are meaningless.

\*\*) The order in which the parameters are read is:

V0, V1, I0, I1, Ramp-up rate, Ramp-down rate, Trip, Channel Status, Channel to Group assignment, VMON, IMON, Conditioning Process Phase, Conditioning Process Time, Channel Type

Here too, the Conditioning Process Phase and Time are meaningful only if the channel belongs to Group A.

- b) For a Global Absolute or Relative Group Selection, the same meanings apply to the subaddresses as for the single channel selection, with the restrictions mentioned for subaddresses 11-12, valid only on Group A.

- c) In a Streamer-tubes-conditioning process Selection :

for targets 40-43, the subaddress (0-15) selects one of the 16 values of the associated parameters (e.g.for Target = 40, subaddress = 3 selects V3).

for targets 44-48, the subaddress is ignored.

d) For a Protection Bits readout Selection the subaddress is ignored.

#### 2.4 READ VALUE(S)

Read value(s) is performed by two Read Cycles: <u>Read</u> at Address 3C, with bits 0-15 of Data Bus containing Data to be read. <u>Read</u> at Address 3E, with bit 0 of Data Bus indicating (if equal to 0) validity of data just read.

These two Cycles must be repeated until bit 0 of Data Bus at Address 3E is 0. Readout is over when this bit is 1.

#### a) Data format for Group Selection:

If a Group (Global Absolute or Global Relative) is selected, the block of data begins with 3 " pattern" words describing which Channels belong to the Group.

In the first 2 words, and in the lower byte of the third word, each bit represents a Channel of the Crate, the Least Significant Bit of the first word representing Channel 0 and so on to Channel 39. After these initial " pattern " words, as many words follow as the number of Channels belonging to that Group; they contain the value of the selected parameter for the corresponding Channel, i.e. the first word refers to the Channel corresponding to the first bit set to 1 in the 3 initial " pattern " words, and so on (NOTE: the first word could be a negative word).

#### b) Channel Status word's bit pattern:

| bit 0 | OFF                 | (if set to one, channel is OFF, and bit 2 goes to zero)   |

|-------|---------------------|-----------------------------------------------------------|

| bit 1 | Trip                | (if set to one, channel was switched off because of Trip) |

| bit 2 | ON                  | (if set to one, channel is ON, and bit 0 goes to zero)    |

| bit 3 | <b>Over-Voltage</b> | (if set to one, channel is in OVV at time of reading)     |

| bit 4 | Under-Voltage       | (if set to one, channel is in UNV at time of reading)     |

| bit 5 | Over-Current        | (if set to one, channel is in OVC at time of reading)     |

| bit 6 | Ramp-up             | (if set to one, channel is undergoing a R-UP phase)       |

| bit 7 | Ramp-down           | (if set to one, channel is undergoing a R-DW phase)       |

|       | A                   |                                                           |

## c) Channel to Group assignment word's bit pattern:

bit 0 set to 1 means that the Channel belongs to Group ALL, bit 1 set to 1 means that the Channel belongs to Group A and so on up to bit 7 which corresponds to Group G.

## d) Channel Type word's bit pattern:

| Positive Channel   | bit  | 7   | OFF |

|--------------------|------|-----|-----|

| Negative Channel   | bit  | 7   | ON  |

| 800 Volts - 500 mA | bits | 1,2 | ON  |

| 2 KVolts - 3 mA    | bit  | 0   | ON  |

| 3 KVolts - 3 mA    | bit  | 1         | ON | or bits 1,2,30N    |

|--------------------|------|-----------|----|--------------------|

| 4 KVolts - 2 mA    | bits | 0,1       |    | or bits 0,1,2,3 ON |

| 6 KVolts - 1 mA    | bits | 0,2       | ON | or bits 2,3 ON     |

| 8 KVolts - 500 μA  | bit  | 2         | ON |                    |

| 8 KVolts - 200 µA  | bits | 0,1,2     | ON | or bits 1,4 ON     |

| 6 KVolts - 200 μA  | bit  | 3         | ON |                    |

| 4 KVolts - 200 μA  | bits | 0,1,3     | ON |                    |

| 2 KVolts - 200 µA  | bits | 1,3       | ON |                    |

| 200 Volts - 200 µA | bits | 0,3       | ON |                    |

| Special Module     | bits | 0,2,3     | ON |                    |

| 800 Volts - 200 μA | bits | 4         | ON |                    |

| 10 KVolts - 1 mÅ   | bits | 0,1,4     | ON |                    |

| 10 KVolts - 200 μA | bits | 1,2,4     | ON |                    |

| 15 KVolts - 200 µA | bits | 0,1,2,4   | ON |                    |

| 15 KVolts - 1 mÅ   | bits | 3.4       | ON |                    |

| I/O - Module       | bits | 0,1,2,3,4 | ON |                    |

e) Protection Status word's bit pattern:

| bit | 0 | Power ON                          |

|-----|---|-----------------------------------|

| bit | 1 | Password enabled                  |

| bit | 2 | Keyboard enabled                  |

| bit | 3 | Alarm*                            |

| bit | 4 | if 0, V0 active - if 1, V1 active |

| bit | 5 | if 0, 10 active - if 1, 11 active |

| bit | 6 | Alarm*                            |

- bit 7 if 0, HV-ENABLE is OFF if 1, HV-ENABLE is ON

- \* They both have the same meaning: Alarm signal for OVV, UNV, TRIP in any one of the channels of the system SY 127 which has been called (see note in the Alarm bit p.8).

### f) Streamer-tubes-conditioning phase: bit pattern

|     | 0-3 | sequential number of the phase (0 to 15 max)                                                  |

|-----|-----|-----------------------------------------------------------------------------------------------|

| bit | 5   | if $= 1$ , means that the conditioning process was terminated by                              |

|     |     | time-out occurence                                                                            |

| bit | 6   | if = 1, means that the channel is undergoing a "recovery " at                                 |

|     |     | zero voltage (this lasts Time-Low(N) seconds, where $N = phase$ number as given by bits 0-3 ) |

|     | _   |                                                                                               |

| bit | 7   | if $= 1$ , means that the conditioning process is active                                      |

#### **IMPORTANT:**

The setting of the Data Bus Lines in Read Cycles depends on the HV module on which one has to act as well as on the operation to be performed. Refer to Chapter 2.5 for details.

#### 2.5 DATA BUS LINES INTERPRETATION (SY 127)

The setting (Write Cycle) and conversely the values (Read Cycles) present on the Data Bus, depend on the characteristics of the specific HV module which is used and on the "target" which has been specified with the "SELECT TARGET" operation (i.e. Group of channels or Single Channel - refer to Chapter 2.1 for details).

In particular, in Write Cycles only, bit 14 of the data field has a specific meaning (note that no H.V. value can be high enough to affect this bit ).

Bit 14 ON means that the H.V. value has to be divided by 10 (i.e. you set a value in tenth of a Volt or in hundredths of a Volt instead of in Volts).

Bit 15 is the sign bit: when set to 1 in write cycle the bits 0-13 of the Data Bus, representing the H.V. value, are coded in binary twos-complement.

CAUTION: bit 14 is not affected by the value of bit 15, i.e. it is never complemented to 2.

#### 2.5.1 HV and RAMP setting and read-out

a) The following HV modules feature a 1/10 Volt resolution:

200 V - 200 μA 800 V - 500 μA

For these modules, the Data Bus Lines in Read Cycles always report a value in tenth of a Volt, irrespective of the bit 14 setting and of the target selected.

For the Data Bus Lines in Write Cycles, the voltage unit implied depends on the target as well as on the setting of bit 14, according to the following table:

a.1) Single Channel Target Selection

| bit 14 OFF unit = $1/10$ | Volt           |        |

|--------------------------|----------------|--------|

| (e.g. DBus = 32 ==>      | V0 = 3.2 Volts | "write |

| V0 = 3.2 Volts ==>       | DBus = 32)     | "read  |

bit 14 ON unit = 1/100 Volt (the H.V. value set is rounded to the highest 1/10 V value below, (e.g. DBus = 64 ==> V0 = 0.6 Volts "write V0 = 0.6 Volts ==> DBus = 6) "read a.2) Group (Absolute or Relative) Target Selection

| bit 14 OFF unit = 1 Volt<br>(e.g. DBus = 17 ==><br>V0 = 17 Volts ==> | t<br>V0 = 17 Volts<br>DBus = 170)    | "write<br>"read |

|----------------------------------------------------------------------|--------------------------------------|-----------------|

| bit 14 ON unit = 1/10 V<br>(e.g. DBus = 17 ==><br>V0 = 1.7 Volts ==> | Volt<br>V0 = 1.7 Volts<br>DBus = 17) | "write<br>"read |

b) The following HV modules feature a 1/2 Volt resolution:

2 KV - 200 μA 2 KV - 3 mA

For these modules, the Data Bus Lines in Read Cycles always report a value in half-volts, i.e. the actual voltage in Volts is the number encoded on Data Bus divided by 2.

The conversion table for the Data Bus in Write Cycles follows:

DBus = 17 ==> V0 = 0.5 Volts ==>

#### b.1) Single Channel Target Selection

| bit 14 OFF unit =<br>(e.g. DBus = 16 =<br>V0 = 8 Volts = |                             | "write<br>"read |

|----------------------------------------------------------|-----------------------------|-----------------|

| bit 14 ON unit =                                         | 1/20 Volt                   |                 |

| (the H.V. value set is re                                | ounded to the highest $1/2$ | V value below,  |

| (e.g. $DBus = 22 =$                                      |                             |                 |

| V0 = 1.0 Volts =                                         | => DBus = 2)                | "read           |

V0 = 0.5 Volts

DBus = 1)

"write

"read

b.2) Group (Absolute or Relative) Target Selection

| bit 14 OFF unit =    | 1 Volt |                |        |

|----------------------|--------|----------------|--------|

| (e.g. $DBus = 100 =$ | =>     | V0 = 100 Volts | "write |

| V0 = 100 Volts =     | =>     | DBus = 200)    | "read  |

| bit 14 ON unit = $1/10$ Vo        |                |        |

|-----------------------------------|----------------|--------|

| (the H.V. value set is rounded to |                |        |

| (e.g. $DBus = 32 = =>$            | V0 = 3.0 Volts |        |

| V0 = 3.0  Volts ==>               | DBus = 6)      | "read  |

| DBus = 37 ==>                     | V0 = 3.5 Volts | "write |

| V0 = 3.5 Volts ==>                | DBus = 7)      | "read  |

Note:

when selected in Absolute Group, the Voltage resolution of the 2 KV-200  $\mu$ A modules depends on the H.V. value itself, namely:

| for | 0 V    | < | H.V. | < | 1639.0 V | resolution = $1/2$ V |

|-----|--------|---|------|---|----------|----------------------|

| for | 1638 V | < | H.V. | < | 2000.0 V | resolution = $1 V$   |

In the range 1638-2000 Volts, a 1/2 Volt resolution can be obtained if the modules are selected as a Relative Group.

c) The following HV modules feature a one-Volt resolution:

| 8 KV - 200 μA | 8 KV - 500 μA   |

|---------------|-----------------|

| 6 KV - 200 μA | 6 KV - 1 mÅ     |

| 4 KV - 200 μA | 3/4 KV - 2/3 mA |

For these modules, the value read in the Data Bus has always to be interpreted as Volts.

For the Data Bus Lines in Write Cycles, there is no distinction due to the target selection mode, but only a dependence on the setting of bit 14, according to the following table:

| bit 14 OFF unit =<br>(e.g. DBus = 50<br>V0 = 50 Volts                                            | ==> V0 = 50  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

| bit 14 ON unit = 1/10 Volt<br>(the H.V. value set is rounded to the highest integer value below, |              |  |  |  |  |  |  |

| (e.g. DBus = $105$                                                                               | => V0 = 10   |  |  |  |  |  |  |

| V0 = 1 Volts                                                                                     | ==> DBus = 1 |  |  |  |  |  |  |

#### 2.5.2 SETTING and READ-OUT of the current

The HV modules with a 1/10 of a  $\mu$ A current resolution follow the same rules as stated for the modules with a 1/10 Volt voltage resolution and those with 1  $\mu$ A follow the rules for 1 Volt.

## 3. VME CYCLES (referring to the SY 227 system)

The necessary VME Cycles for every sequence are detailed. In the following, bits A23-A6 are ignored. Refer to the SY 127 System Manual for further information and for the meaning of the Channels' parameters.

#### 3.1 SELECT TARGET

Select Target is performed by two Write Cycles: <u>Write</u> at Address 18, with bits 0-7 of Data Bus selecting the desired target and bits 8-15 specifying the number (between 0 and 99) of a Crate in the SY-127 System.

Write at Address 1A, with bits 0-15 of Data Bus ignored.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1A:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation; bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not accepted, in this case repeat the action performed; bits 1to 15 of Data Bus (DB1to DB15) are ignored.

Crate numbers 100 to 255 are reserved to the System. An invalid crate number at this stage is immediately reported as an error code -1.

The value of the lower byte of the Data Bus Lines is interpreted as follows:

- **0-31** gives the number of channels selected on each distribution board for single channel operations;

- 50 for operations common to all the channels on the selected slot;

- 70 for operations on the system protection bits (the protection reading requires no subaddress).

#### 3.2 WRITE DATA

Write Data is performed by two Write Cycles:

<u>Write</u> at Address IC, with bits 0-15 of Data Bus containing Data to be written.

<u>Write</u> at Address 1E, with bits 0-3 of Data Bus containing the subaddress which selects the parameter to write.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1E:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation;

bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not

accepted, in this case repeat the action performed; bits 1to 15 of Data Bus (DB1to DB15) are ignored.

a) For a single channel selection (Target = 0-31 in the select target operation) only subaddresses 0 and 3 are allowed.

The meaning of the subaddresses is the following:

- 0 Slot selection (see note (o) 3.5)

- 3 IMAX (see note (ii) 3.5)

Use of subaddresses different from 0 and 3 give an error (see Error Codes).

b) For operations referring to all the channels on the selected slot (Target = 50); only subaddresses 0, 3, 5 and 6 are allowed.

The meaning of the subaddresses is the following:

- 0 Slot selection (see note (o) 3.5)

- 2 Zero Current Set (see note (x) 3.5)

- 3 IMAX (see note (ii) 3.5)

- 5 ON/OFF HV (see note (iii) 3.5)

- 6 EN/DIS pulse test (see note (iv) 3.5)

Use of subaddresses different from 0, 3, 5 and 6 give an error (see Error Codes).

c) For operation referring to the Protection Bit selection (Target = 70). Subaddress is ignored, and only the first bit of the data field is used (see note (v) 3.5).

Any attempt to write a bit different from 0 gives an error (see Error Codes).

#### 3.3 START READOUT

Start Readout is performed by two Write Cycles:

<u>Write</u> at Address 18, with bits 0-7 of Data Bus ignored and bits 8-15 all set to 1.

<u>Write</u> at Address IA, with bits 0-3 of Data Bus containing the subaddress which selects the parameter to read.

To test validity of the action performed, it is necessary to perform a Read Cycle at Address 1A:

bit 0 of Data Bus (DB0), if equal to 0, indicates accepted operation;

bit 0 of Data Bus (DB0), if equal to 1, indicates that the operation is not accepted, in this case repeat the action performed;

bits 1to 15 of Data Bus (DB1to DB15) are ignored.

For a single channel selection (target = 0 - 31). a)

The subaddress meaning is:

- 0 Slot number (see note(o) 3.5)

- 1 VMON (see note(vi) 3.5)

- 2 IMON (see note (ii) 3.5)

- 3 IMAX (see note (ii) 3.5)

- 7 Status (see note (viii) 3.5)

- 15 selects the readout of all the parameters in a block\*

- The order in which the parameters are read is : Slot Number, VMON, IMON, IMAX, \* STATUS.

Use of different subaddresses from those above will give error (see Error Codes).

- For operations referring to all the channels on the selected slot (target = 50) (see 3.4 b) Read Values). The subaddress meaning is:

- 0 HV boards present in the crate (see note (i) 3.5)

- 1 VMON (see note (vi) 3.5)

- 2 IMON (see note (ii) 3.5) 3 IMAX (see note (ii) 3.5)

- 4 HV IN status (see note (vii) 3.5)

- 5 HV ON/OFF (see note (iii) 3.5)

- 6 Pulse test (see note (iv) 3.5)

- 7 Status (see note (viii) 3.5)

- 8 Number of channels on the slot

- 9 Current resolution (see 3.4)

- 10 Full scale current (see note (ii) 3.5)

- 11 Voltage resolution (see 3.4)

- 12 VMAX (see note (vi) 3.5)

- 13 HV IN polarity (see note (ix) 3.5)

- 15 All parameters\*.

- The order in which the parameter are read is : HV Board, VMON, IMON, IMAX, HV IN \* status, HV ON/OFF, Pulse Test, STATUS, Number of channels, Current resolution, Full Scale, Voltage resolution, VMAX, HV IN polarity.

Use of different subaddresses from those above will give error (see Error Codes).

For operation referring to the Protection Bit selection (Target = 70). Subaddress is ignored, c) and only the first bit of the data field is used (see previous (v) note).

#### 3.4 READ VALUE(S)

Read value(s) is performed by two Read Cycles: Read at Address 3C, with bits 0-15 of Data Bus containing Data to be read. **Read** at Address 3E, with bit 0 of Data Bus indicating (if equal to 0) validity of data just read.

These two Cycles must be repeated until bit 0 of Data Bus at Address 3E is 0.

#### Readout is over when this bit is 1.

Data format for all channels on the selected slot:

If all channels are selected, the block of data begins with 1 "pattern" word which is always the slot number.

After these initial "pattern" words, as many words follow according to the selected parameter:

VMON, IMON, IMAX and Status have as many pattern words as channels on the slots;

Current resolution, Voltage resolution : have two pattern words:

the first pattern is the value, the second is the unit measurement in ASCII code (in the least significant 8 bits the A(amps) or V(voltage) character is read, in the most significant 8 bits you can read 'n' (nano) or 'u' (micro) or 'm' (milli) or Blank;

All the other parameters have only one pattern word.

#### 3.5 DATA BUS LINES Interpretation (SY 227)

#### Notes:

(o) In the slot selection the Data Bus lines mean the following:

Data Bus line = 0 slot 1 Data Bus line = 1 slot 2 Data Bus line = 2 slot 3 Data Bus line = 3 slot 4

Use of different bits gives an error. (see Error Code)

(i) In the HV board selection the Data Bus lines when equal to one have the following meaning:

Bit 0 = slot 1 present;Bit 1 = slot 2 present;Bit 2 = slot 3 present;Bit 3 = slot 4 present.

The number of the slots runs from high to low.

- (ii) The data to be written or read are the absolute value divided by the current resolution of the board.

- e.g. If you wish to set the IMAX value equal to 800 nA in a board which has a current resolution of 5 nA, the data will be equal to  $800 \div 5 = 160$ .

Use of different bit in the write line gives an error. (see Error Code)

(iii) H.V. ON/OFF:

In write data only bit 0 is significant. In read value bit 0 and bit 1 are significant.

> Bit 0 = 1 (H.V. Relay ON) Bit 0 = 0 (H.V. Relay OFF) Bit 1 = 1 (switch ON) \* Bit 1 = 0 (switch OFF)

Any attempt to write a bit different from 0 gives an error. (see Error Codes).

\* It is possible to recognize the change of the status of the manual switch only if there is High Voltage in the input.

#### WARNING:

It is possible to turn on the Relay only if the input does not have High Voltage.

- Any attempt to switch on the Relay in this case gives an error (see Error Codes).

- (iv) In the EN/DIS pulse test only bit 0 is significant.

Bit 0 = 1 (Pulse Test Enable) Bit 0 = 0 (Pulse Test Disable)

Use of different bits gives an error. (see Error Code)

(v) In changing the Protection Bit selection, subaddress is ignored, and only the first bit of the data field is used.

Bit 0 = 1 (Password Enable) Bit 0 = 0 (Password Disable)

Use of different bits gives an error. (see Error Code)

- (vi) The read value is absolute.

- (vii) In the HV IN status selection the Data Bus lines mean the following:

Data Bus line = 0: no HV present in the input. Data Bus line = 1: positive HV in the input. Data Bus line = 2: negative HV in the input.

(viii) In the STATUS selection the Data Bus lines bit 0, bit 1, bit 2, bit 3 and bit 8 when equal to one have the following meaning:

Bit 0 = 1 (fixed) Bit 1 = OVC (overcurrent) Bit 2 = OFS (over full scale) Bit 3 = OMV (over max voltage) Bit 8 = SY 227 (when Bit 8 = 0: SY 127).

(ix) In the HV IN polarity selection the Data Bus lines mean the following:

Data Bus line = 0: negative and positive polarity. Data Bus line = 1: positive polarity. Data Bus line = 2: negative polarity.

(x) In the Zero Current Set bits 0 to 15 of the Data Bus in the write cycle must equal 1.

#### 4. RESET

RESET is made via a <u>Write</u> Cycle at Address 28 with Data Bus bits 0-15 ignored.

To be sure that the action has been successful, a Read Cycle at the same Address is suggested. The meaning of Data Bus bit 0 is the same as in the other actions.

A 200 supports also hardware RESET by VME System.

After a RESET Command has been issued, a wait time of at least 300 msec has to be introduced before any other VME Cycle can be successfully performed on the system.

## 5. READ VALIDITY of actions

A response is given to each VME Cycle supported by the Interface.

A Data Bus bit 0 = 1 response means that the A200 is busy, and that the action has been rejected: it has to be repeated until a Data Bus bit 0 = 0 response is obtained.

On the other hand, during readout, data are valid only when Data Bus bit 0 = 0, and will continue to be valid until Data Bus bit 0 becomes 1.

If a single negative word is obtained in a READ VALUE operation, this is interpreted as an error code.

After each Write Cycle, it is wise to perform a READ VALUE operation to read the relative error code (see Chapter 3 for a comprehensive list of the errors).

## 6. ERROR CODES

- 0 successful operation

- -1 invalid assignement of a Channel or Crate number

- -2 attempt to START READOUT without previous SELECT TARGET

- -3 attempt to WRITE DATA without previous SELECT TARGET

- -32 channel selected non-existent

- -33 attempt to write a too small a parameter value

- -34 attempt to write a too large a parameter value

- -48 selection of non implemented function

- -256 selection of non-existent crate

## ERROR CODES VALID FOR THE SY 127 SYSTEM:

- -4 attempt to change a Status bit different from ON/OFF

- -5 attempt to write a Read-only parameter (Subaddress > 8)

- 6 attempt to assign a Channel to a non-existent Group (the Groups are represented by the first 8 bits of the Data Bus Lines, and a bit higher than 7 has been used)

-7 attempt to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Total Width Time of the Streament to write the Streament to

- attempt to write the Total Width Time of the Streamer-tubes-conditioning

attempt to Start, Stop, Pause the Streamer-tubes-conditioning process.

- (this can only be done from a terminal directly connected to the system)

- -9 during Absolute Group Selection, attempt to write with A>7.

- -10 attempt to use a bit different from 0 when writing a Status

- -11 during Relative Group Selection, attempt to write with A>6.

- -12 error on setting protection bit

## ERROR CODES VALID FOR THE SY 227 SYSTEM:

- 35 attempt to change ON/OFF HV different from bit 0

- 36 attempt to switch-on with HV IN present

- 37 attempt to change Pulse Test EN/DIS different from bit 0

- 38 attempt to change Password EN/DIS different from bit 0

#### NOTE:

Error codes different from those referring to the selected system are not significant.

# For SY 127 6.0 Software version and/or previous software versions:

The user cannot turn on the channels as a first operation when working in Group mode (ERROR -33)

In order to transfer the channel assignment performed via VME into the non-volatile memory (EEPROM) the user must check on the Terminal (via RS 232) if the assignment is correct.

1

APPENDIX A: COMPONENTS LIST AND LOCATION

and the second

| Item | Quantity | Reference                                             | Part                     |

|------|----------|-------------------------------------------------------|--------------------------|

| 1    | 1        | C1                                                    | 82pF                     |

| 2    | 2        | C3,C2                                                 | 2.2uF/16V                |

| 3    | 1        | C49                                                   | 2.2nF                    |

| 4    | 1        | C64                                                   | lOnF                     |

| 5    | 49       | CF1CF49                                               | 100nF                    |

| 6    | 1        | D1                                                    | 1N4002                   |

| 7    | 1        | D2                                                    | YELLOW LED               |

| 8    | 1        | D3                                                    | GREEN LED                |

| 9    | 1        | DL                                                    | RED LED                  |

| 10   | 1        | D4                                                    | 1N314                    |

| 11   | 2        | D5,D6                                                 | DIP-SWITCH 8 VIE         |

| 12   | 1        | D7                                                    | DIP SWITCH 2 VIE         |

| 13   | 1        | J1                                                    | LEMO00                   |

| 14   | 3        | JP1, JP2, JP3                                         | JUMPER                   |

| 15   | 1        | P1                                                    | EURO.CONN.96 PIN (a+b+c) |

| 16   | 1        | Q1                                                    | BD512                    |

| 17   | 1        | Q2                                                    | BC328                    |

| 18   | 2        | 10P1,10P2                                             | PACKAGE 10 PIN 2.2K      |

| C    | 2        | R1,R2                                                 | 47K                      |

| 20   | 14       | R4,R3,R5,R6,R9,R10,R11,R12<br>R13,R21,R26,R27,R28,R30 | 2.2K                     |

| 21   | 1        | R7                                                    | 1.5K                     |

| 22   | 1        | R8                                                    | 5.6K                     |

| 23   | 1        | R14                                                   | 4.7                      |

| 24   | 2        | R17,R18                                               | 10K                      |

| 25   | 1        | R19                                                   | 4.7K                     |

| 26   | 1        | R20                                                   | 220                      |

| 27   | 1        | R22                                                   | 100                      |

| 28   | 3        | R23,R24,R25                                           | 1K                       |

| 29   | 1        | R29                                                   | 330                      |

| 30   | 1        | SW1                                                   | PUSHBUTTON               |

|              | -H.V. CAENET VME CONTROLLER - Mod. A200 Component List revised: Nov, 30 1990 |          |                        |                          |  |

|--------------|------------------------------------------------------------------------------|----------|------------------------|--------------------------|--|

| *            | Item                                                                         | Quantity | Reference              | Part                     |  |

|              | 31                                                                           | 1        | U1                     | 74S38                    |  |

|              | 32                                                                           | 6        | U3,U33,U36,U46,U50,U54 | 74LS244 Kistungstreik of |  |

| •            | 33                                                                           | 2        | U4,U5                  | 74LS138                  |  |

| • •          | 34                                                                           | 1        | UG                     | 4020                     |  |

|              | 35                                                                           | 2        | U8,U52                 | 74LS257                  |  |

| -            | 36                                                                           | 1        | U9                     | 74LS02                   |  |

| -            | 37                                                                           | 1        | U10                    | 74LS123                  |  |

| -            | 38                                                                           | 1        | U11                    | 16R4                     |  |

| •            | 39                                                                           | 3        | U12,U22,U56            | 74LS74                   |  |

| -            | 40                                                                           | 1        | U13                    | 8259A                    |  |

| -            | 41                                                                           | 1        | U14                    | 74S188                   |  |

| - <b>-</b> ) | 42                                                                           | 1        | U15                    | 2651                     |  |

|              | 43                                                                           | 1        | U16                    | 4049                     |  |

| -1           | 44                                                                           | 1        | U18                    | 74F373                   |  |

|              | 45                                                                           | 1        | U21                    | 16L8                     |  |

| -1           | 46                                                                           | 1        | U23                    | 74LS373                  |  |

|              | 47                                                                           | 3        | U26,U29,U61            | 74ALS534                 |  |

|              | 48                                                                           | 2        | U32,U35                | 74F244                   |  |

|              | 49                                                                           | 4        | U31,U7,U25,U28         | 74LS161                  |  |

| J            | 50                                                                           | 3        | U37,U34,U42            | 6116                     |  |

|              | 51                                                                           | 1        | U38                    | 2764                     |  |

| -            | 52                                                                           | 3        | U41,U39,U40            | 74ALS521                 |  |

|              | 53                                                                           | 1        | U45                    | 74LS08                   |  |

| -            | 54                                                                           | 1        | U49                    | 74LS00                   |  |

|              | 55                                                                           | 2        | U47,U48                | 74LS374                  |  |

|              | 56                                                                           | 1        | U51                    | 8257                     |  |

| -            | 57                                                                           | 1        | U53                    | 8085                     |  |

| -            | 58                                                                           | 1        | U55                    | 74LS240                  |  |

|              | 59                                                                           | 2        | U60,U24                | 20L8                     |  |

| J            | 60                                                                           | 1        | X1                     | 6.144 MHz QUARZ          |  |

Appendix B: Electrical Diagrams