## Mueller, Carsten

Von: Geissler, Rene

Gesendet: Freitag, 15. März 2024 17:12

An: Mueller, Carsten Cc: Braisz, Lukas

Betreff: AW: MAPS-Adapterbox

Hallo Carsten,

zu deiner Frage "Gib das Web was her ob man das Mapping pro CPLD nur einmal festlegen kann?":

Das ist ein Bug in ISE und hat nichts mit dem nur einmal Festlegen zu tun. Ich habe dafür keine Lösung. Möglicherweise hatte es einen Grund, warum Xilinx seine CPLDs eingestellt hat. Bitte selbst nochmal verifizeren (im UCF-File des CPLD 2 die Pinzuordnung der grünen Zeilen umdrehen, dann auf das grüne Dreieck klicken: -> Absturz beim Fitting).

Viele Grüße

René

Von: Mueller, Carsten

Gesendet: Freitag, 15. März 2024 16:56:07

An: Geissler, Rene Cc: Braisz, Lukas

Betreff: AW: MAPS-Adapterbox

Guten Tag die Herren,

schönen Dank schon mal für den Erfolg gestern das DisplayControl bord (Der Prototyp) erstmalig zum Leben zu erwecken!

(Noch steht die Anzeige auf dem Kopf, dazu später Genaueres)

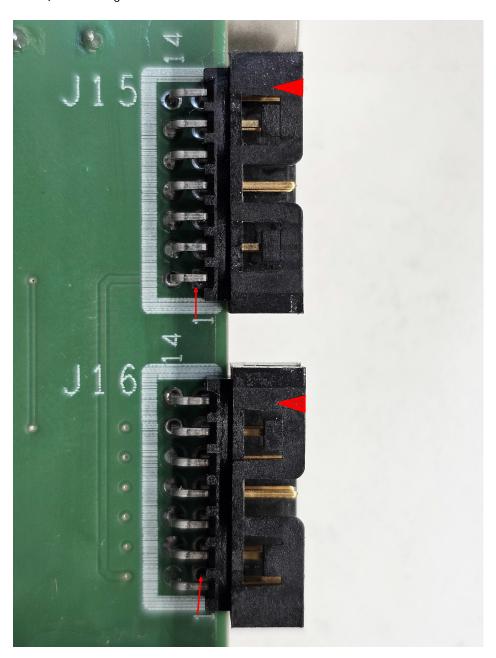

1.) Zum festgestellten Fehler der JTAG- Schnittstellen der CPLDs:

Dies ist ein mir aus Zeitgründen unterlaufener Fehler im Layout: diese Pfostenwanne hat den Pinabstand 2mm statt üblicher 2,54mm. Ich habe auf eine bereits in der ORCAD-Datenbank gerade Variante zurück gegriffen, da in der Regel die Teile für ORCAD innerhalb der zentralen Datenbank abgelegt werden. Die Einpflege der Bauteile nimmt sich die EE vor (Hat Vor- und Nachteile). Eine gerade Pfostenwanne hätte man auf dem Board 180° so drehen können, das Pin 1 der codierten Wanne (Dreieck Marke) auch auf dem eckigen Pinloch für Pin1 liegt! Tatsächlich eingesetzt ist nun ja gewollt der Winkelstecker um durch die Blende nach vorne raus zu kommen. Der hätte dann ein anderes Footprint gehabt. Lösung daher: wie bereits festgestellt, Programmierstecker umgekehrt aufstecken! Dazu wird er Codierausbruch der Wanne auch auf der anderen Seite eingeschnitten!

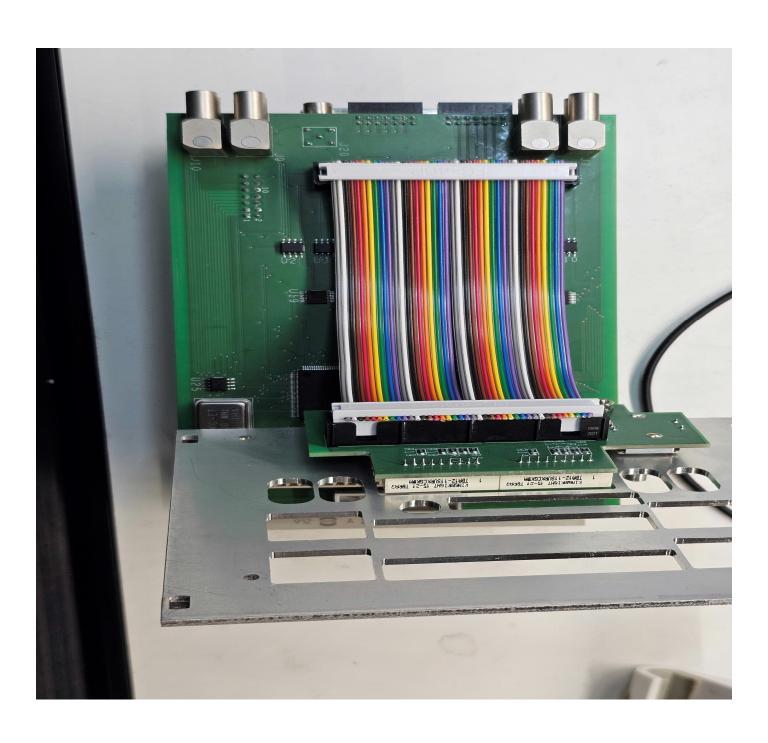

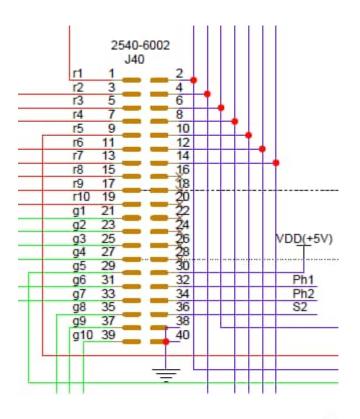

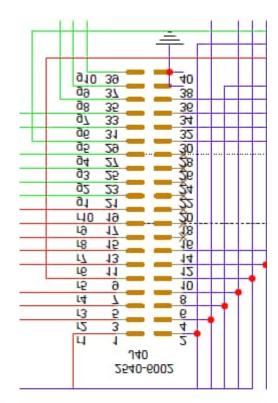

2.) Die Kopfstehende Anzeige: Lukas hat mir netterweise kurzfristig ein Kabel gequetscht, vermutlich liegt da das Kopfstellproblem:

Die schwarzen, 40poligen Pfostenwannen sind mit Ihrer Codierung gleich orientiert auf dem Foto beider Boards, weil "J11" auf dem Basis board

"DisplayControl-V2" auf der Oberseite der Platine ist mit zentraler "Zapfenöffnung" für den Stecker links. Diese Öffnung ist auch in real nach links

orientiert, auch wenn der Ausschnitt des Frontboards anders dargestellt ist in der Oberseitenansicht. Der Pfosten "J14" sitzt auf dem Frontboard

auf der Unterseite des Boards (nach innen orientiert) wie auf dem Foto erkennbar.

Das Flachbandkabel verlässt das Frontboard nach rechts und geht aber von links an das Frontboard ein! Macht das was?

Nein, denn die linke obere Schnittkabel des Pfostensteckers schneidet gleichbleibend in die lila Ader und das egal von welcher Seite!

Dennoch steht die Anzeige Kopf – warum? Wenn man um die horizontale Achse vertikal spiegelt kommt man zum gleichen Ergebnis, welches

Die Anzeigezeilen vertauscht! Aber der Drehcodierer an den Pins 30-36 funktioniert genauso wie geplant!

Da führt schließlich zur Erkenntnis:

Die Datenvorgabe an die LEDs erolgt spaltenweise im Millise so wird zum Beispiel ein Bit eines Messbereichs zweimal in gebracht, wenn die jeweilige Spalte zur Anzeige aktiviert i Damit scheinen die Messbereiche kräftiger zu leuchten, weni sind. Wird ein virtueller Beschleuniger seltener vorgegebei werden dessen Messbereiche schwächer erscheinen!

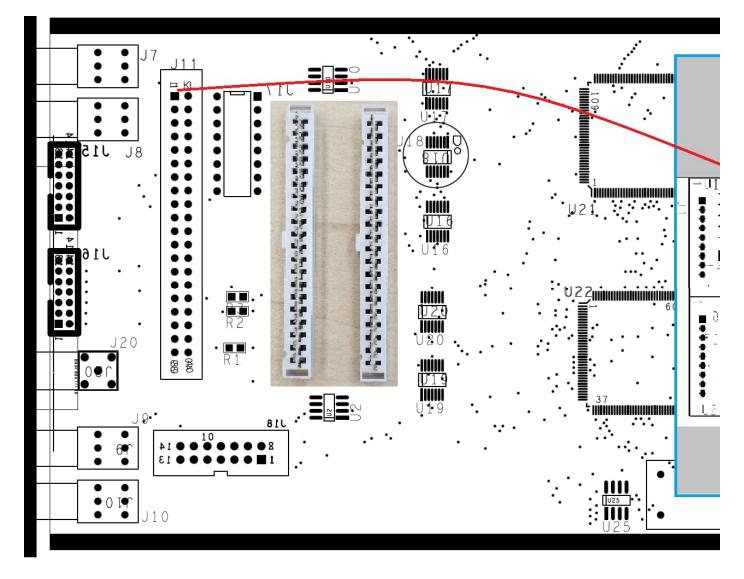

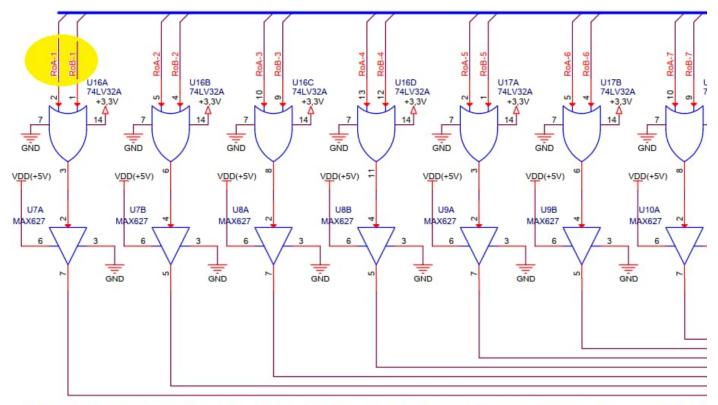

Im Schaltplan ist die Signalzuführung vom CPLD über die Veroderung (jeder CPLD hat Zugriff) auf die LED-Treiber eingangsseitig von links-1 nach rechts indiziert, ausgangsseitig aber umgekehrt von rechts nach links. Das ist leider schon in Hardware des Displaybords vergossen.

## Was also tun:

- In der XILINKS-ISE erfolgt die mit einem "Mapping" die Signalzuordnung an die Ausgabe Pins: theoretisch ließ sich dort die Signalzuordnung aus dem CPLD heraus richtig drehen.

(Bei unserem Versuch gestern hat das nicht geklappt. Kann man bei XILINKS diese Zuordnung nur einmalig festlegen?)

- 2.) Verdrehung im "DisplayControl" board oder dem kleineren und einfacheren Frontbord in neuer Version richtig drehen.

- 3.) Betrachtung im Spiegel! 😊

Das fürs Erste. Gib das Web was her ob man das Mapping pro CPLD nur einmal festlegen kann?

https://www-bd.gsi.de/dokuwiki/doku.php?id=projects:maps21:s:dcontv2-l:dcontv2-l#layout\_displaycontr-v2

Schönes Wochenende,

Carsten

Von: Geissler, Rene <R.Geissler@gsi.de> Gesendet: Donnerstag, 14. März 2024 21:09 An: Mueller, Carsten <Ca.Mueller@gsi.de>

Betreff: AW: MAPS-Adapterbox

## Korrektur:

<< Die Reihenfolge der grünen Spalten ist umgekehrt gegenüber dem Schematic

Die Reihenfolge der Spalten ist umgekehrt gegenüber dem Schematic

Die Spalten betreffen ja glaube ich rot und grün zusammen.

Von: Geissler, Rene

Gesendet: Donnerstag, 14. März 2024 21:00:52

An: Mueller, Carsten; Braisz, Lukas

Betreff: MAPS-Adapterbox

Hallo Carsten, hallo Lukas,

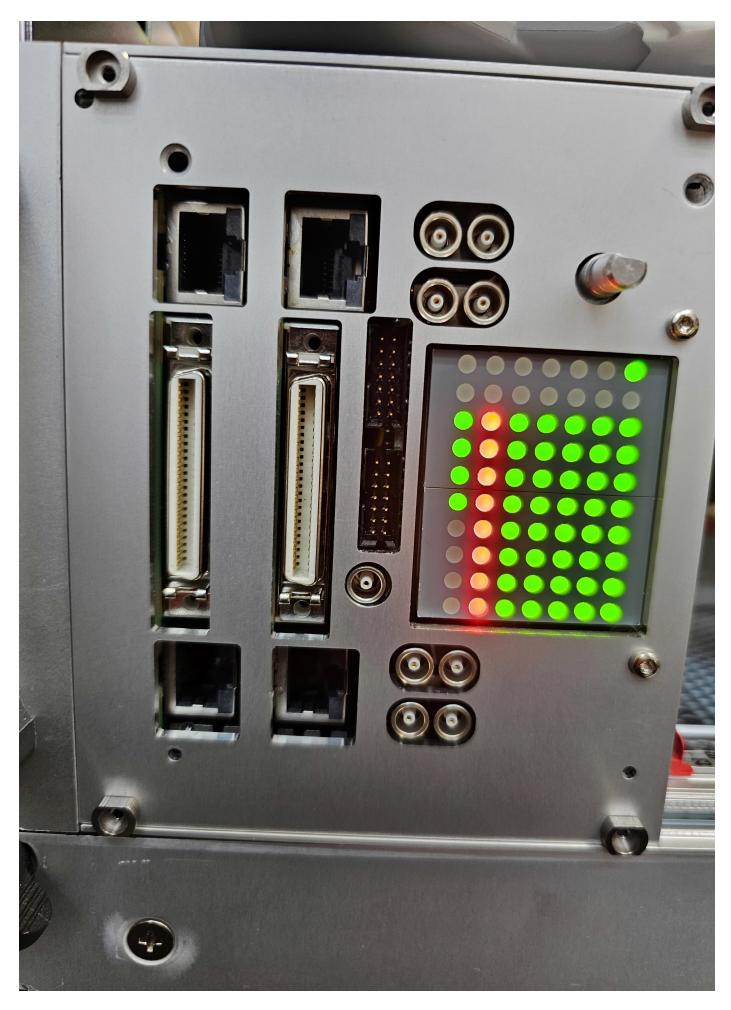

das Leuchtbild, das wir heute gesehen haben, deutet denke ich auf folgende Fehler auf dem PCB oder bei der Verkabelung des Displays hin:

- Die Reihenfolge der grünen Zeilen ist umgekehrt gegenüber dem Schematic

- Die Reihenfolge der grünen Spalten ist umgekehrt gegenüber dem Schematic

- Wir haben heute eine rote 6. LED-Spalte gesehen. Ich habe noch einmal in meinen Code geschaut und dort kann dies definitiv nicht passieren. Die LEDs dort müssen entweder gelb sein (rot und grün leuchten gleichzeitig), oder aus. Dies könnte darauf hindeuten, dass die Reihenfolge der roten LEDs nicht mit vertauscht ist, oder es liegt noch ein anderer Schaltungsfehler vor.

Mein heutiger Versuch, die Reihenfolge durch die CPLD-Logik korrigieren, ist fehlgeschlagen: Es gab reproduzierbar auf Windows und Linux einen Absturz von ISE.

Dies deutet nur darauf hin, dass ISE auf jeden Fall Mist ist. Das fehlerhafte Verhalten von ISE ist mir von früher bekannt. Evtl. könnte es helfen, irgendetwas irrelevantes anderes zu ändern. Der Absturz könnte aber auch auf ein echtes Problem hindeuten, z.B. dass die Signale aus irgendeinem Grund nicht auf diese Weise durch das CPLD geroutet werden können.

Bevor ich weitere Zeit investiere, bitte alle Verbindungen auf dem PCB und zum Display auf Korrektheit überprüfen und gegebenfalls die Nummerierungen im Schematic an die reale Verdrahtung anpassen.

Zur Erinnerung noch der gestern gefundene Fehler: Die Steckverbinder für den Programmer sind in der falschen Richtung verbaut (die Aussparung für die Nase am Stecker ist auf der falschen Seite).

Viele Grüße René

\_\_

Rene Geissler Data Acquisition and Software (DAT)

## Beam Instrumentation (BEA)

Phone / Telefon: +49 6159 71 1302

Fax: +49 6159 71 2104

r.geissler@gsi.de

GSI Helmholtzzentrum für Schwerionenforschung GmbH Planckstraße 1, 64291 Darmstadt, Germany, <u>www.gsi.de</u>

Commercial Register / Handelsregister: Amtsgericht Darmstadt, HRB 1528 Managing Directors / Geschäftsführung: Professor Dr. Paolo Giubellino, Dr. Ulrich Breuer, Jörg Blaurock Chairman of the GSI Supervisory Board / Vorsitzender des GSI-Aufsichtsrats: Ministerialdirigent Dr. Volkmar Dietz