# FAIR Timing System and White Rabbit Project

#### FAIR Technikforum 08.07.2010

### Two distinct, yet tightly coupled systems:

#### General machine timing system

- BEL group

- distributes accelerator events

- distributes absolute time

- defines time standard for CS

- low ns accuracy / synchronization

- One global timing master

$\rightarrow$  this talk

#### BuTiS (bunch phase timing system)

- HF group

- distributes high precision clocks

for rf systems

- sub-ns accuracy / synchronization

- One global BuTiS center

- $\rightarrow$  future talk 28.10.

#### The WR Timing Project (started 2008 by CERN)

- Similar timing systems for different facilities

- Shared development / Open Hardware Repository

- Collaboration: CERN, GSI and others

CERN and CSI will use the same system / to

- $\rightarrow$  CERN and GSI will use the same system / technology

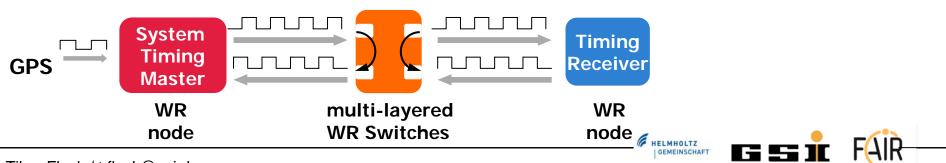

### What is "White Rabbit" ?

"White Rabbit is a fully deterministic **Ethernet-based** field bus for general purpose data transfer and synchronization. [...] The key technologies used are **Synchronous Ethernet** and **PTP** (IEEE1588)."

- WR protocol special layer 2 "WR switches" / "WR nodes"

- Precise time and frequency transfer

- Deterministic frame transmission / fixed switching latency

- High robustness: event loss  $< \sim 10^{-15}$

# FAIR Timing System

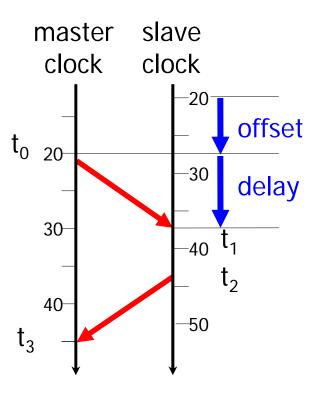

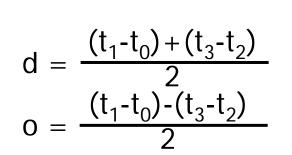

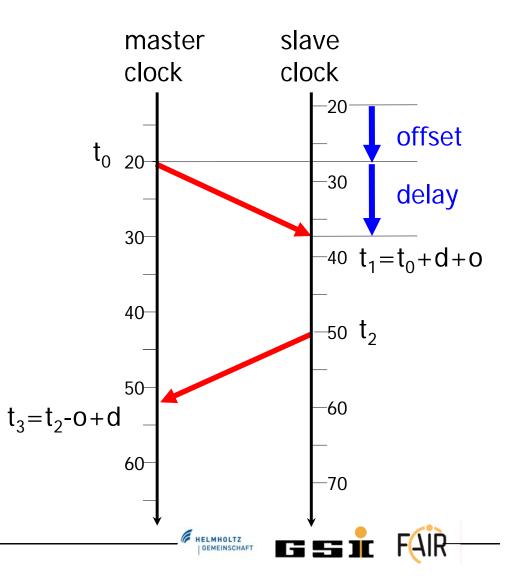

**Precision Time Protocol** ( $\rightarrow$  deliver time of day)

- Use WR handshakes and exact timestamping

- Synchronize local times with master time

- Measure and compensate link delays

# Synchronous Ethernet (→ deliver frequency)

- Nodes use same physical clock

- Clock encoded in Ethernet carrier

- Clock recovered by PHY PLL

#### **Features**

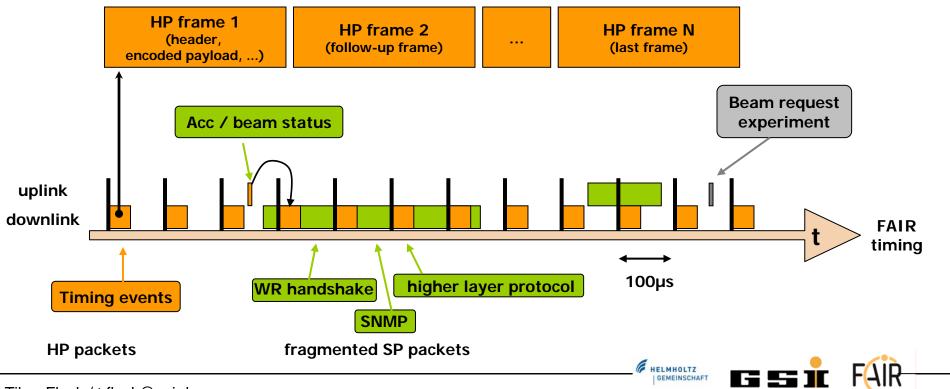

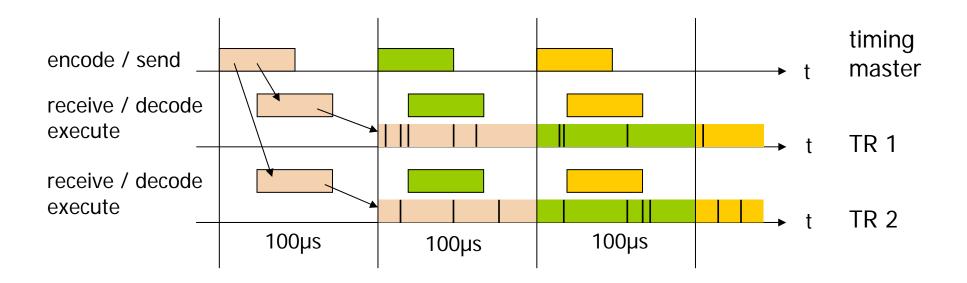

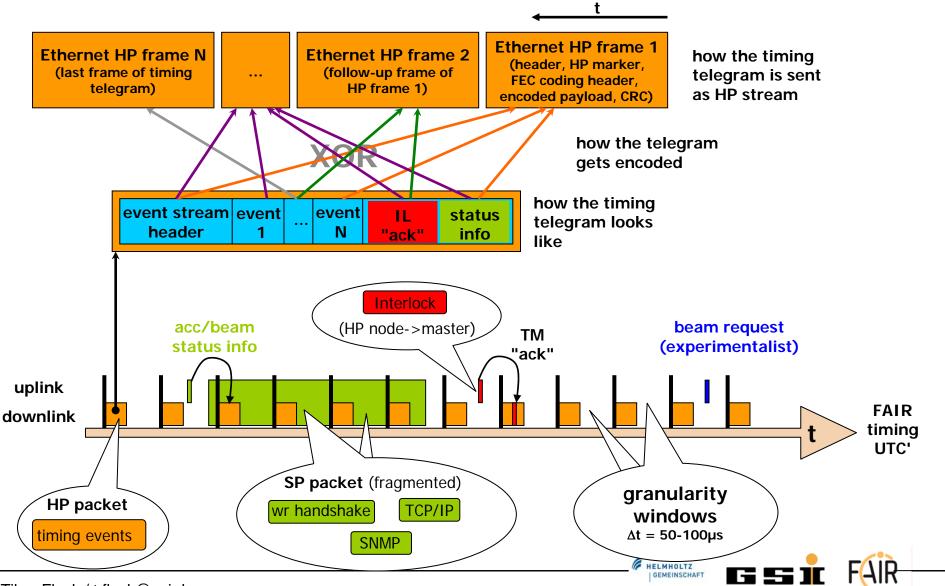

- Timing events broadcasted facility-wide

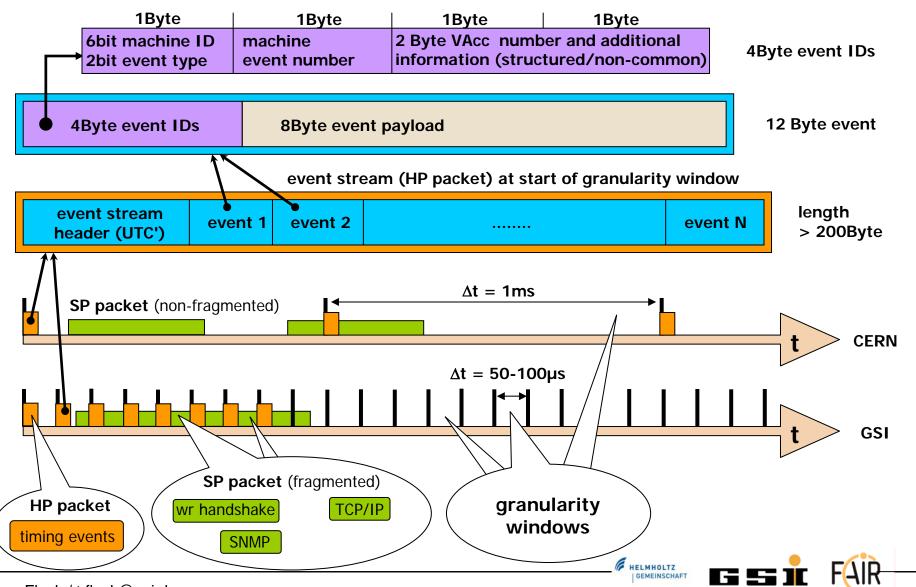

- $\rightarrow$  Events bundled for transmission

- $\rightarrow$  Encoded / "repeated" for robustness

- → Distribution every 100µs

- $\rightarrow$  Distribute event execution times

- Deterministic delay, high reliability

→ high priority "HP" packets

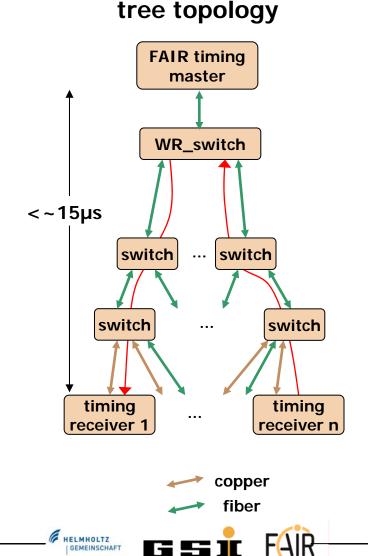

- ~200 WR switches

- ~ 2000 timing receivers

#### **Event distribution**

- Not purely event based !!

- Forward error correction algorithms

#### **Event distribution**

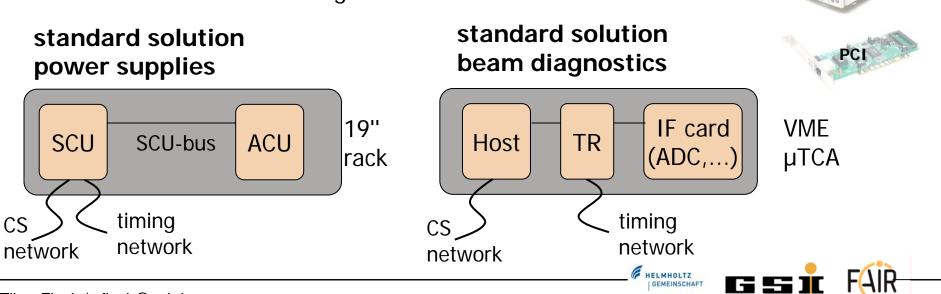

# FAIR Timing System

μΤCΑ

standalone TR

PMC

VME

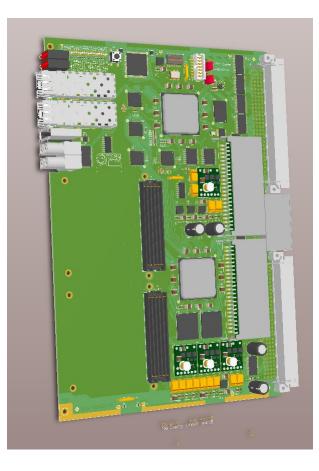

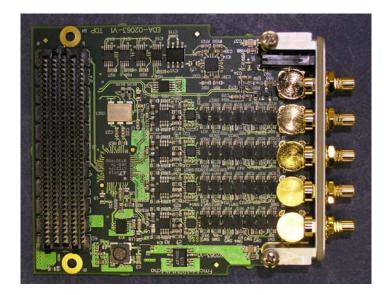

#### WR Timing Receiver (TR) Boards

- Event decoding, postprocessing and filtering

- Absolute notion of time

- Optional Mezzanines on FMC carriers !

- Form factors:

- → SCU (standard FAIR controller)

- $\rightarrow$  VME, PCIe, µTCA, standalone TR

- Full FESA device integration / Linux driver

#### Main enhancements vs. current timing system

- Absolute (UTC related) notion of time in all TRs

- Parallel event execution / no minimal event separation

- Bidirectional communication possible (node  $\rightarrow$  master)

- Huge bandwidth / facility-wide event distribution

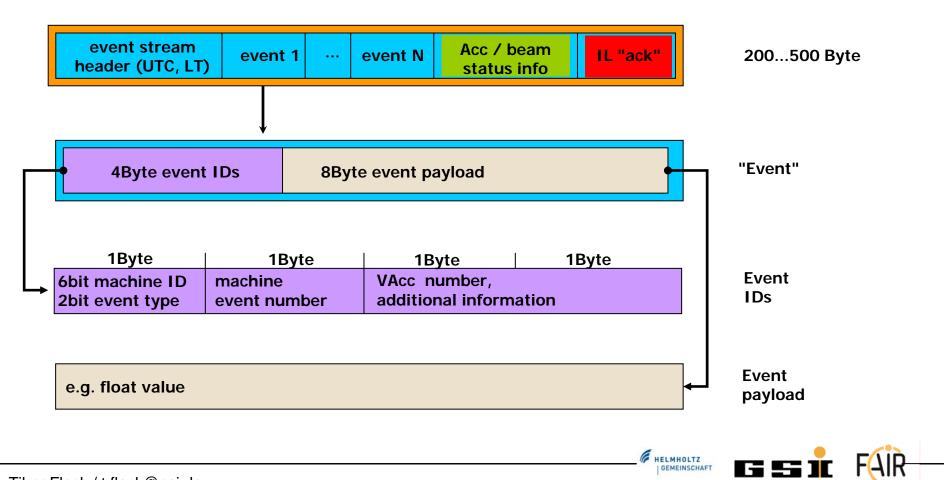

- Large event content (4 Byte header info / 8 Byte payload)

- Transmission of frequencies possible ( $\rightarrow$  BuTiS 100kHz clock)

- Potential to be used for further deterministic and reliable communication

→ online beam information, interlock transmission ... 2 b explored

Thanks for your attention...

### ... let's have some good discussion now

→ it's still possible to have some influence on the concepts

#### **Event packet content**

#### VME timing receiver

4 channel 100MSPS 14 bit ADC mezzanine card

#### White Rabbit Protocol

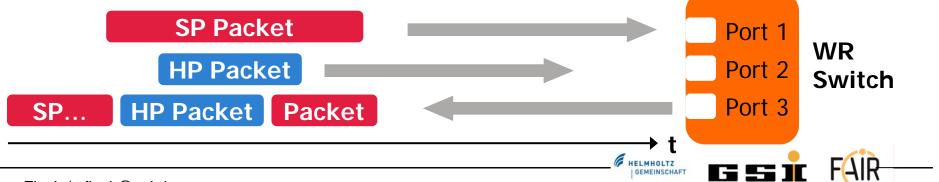

• Ethernet traffic split into:

High Priority(HP) packetsStandard Priority(SP) packets

- HP packets use special value Ethertype field in frame

- HP packets preempt other packets "on-the-fly"

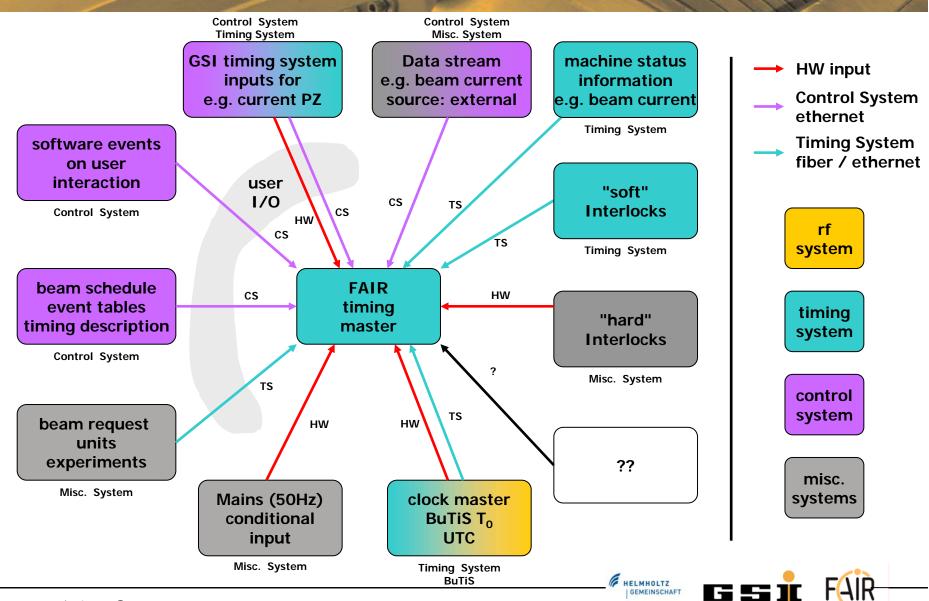

#### **FAIR** Timing Master

- Central powerful hardware

- Fully FESA compliant device

- Real time parallel event scheduling in FPGA

- Event stream generation / encoding

### **WR Timing Switches**

- PTP handling

- Layer 2 port management

- Precise timestamping

- High precision clock / phase measurement

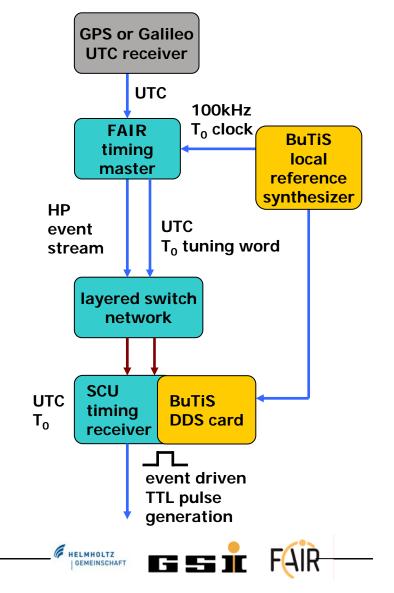

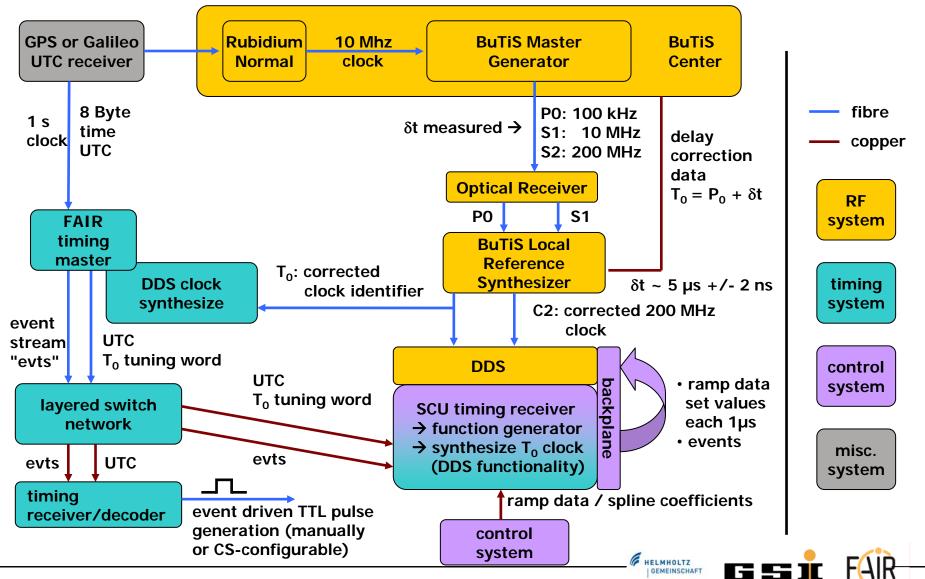

# FAIR Timing System BuTiS Integration

# **BuTiS Architecture:**

- High precision 10/200MHz rf clocks

- 100kHz clock

### **Problem: different time domains**

# **Solution: Distributed DDS**

- Timing Master samples BuTiS clock

- Timing network fully

transparent to BuTiS clock

- Distribution of "tuning words"

- Timing receivers resynthesize

100kHz BuTiS clock

- Accuracy < 1ns

### Correlation between the rf BuTiS system and the timing system at FAIR

# FAIR Timing System

# Precision Time Protocol

$(\rightarrow$  deliver time of day)

- Synchronize local times with master time

- Measure and compensate link delays

- Use WR handshakes and exact timestamping

# timing event messages granularity windows concept

### timing event messages / content granularity windows

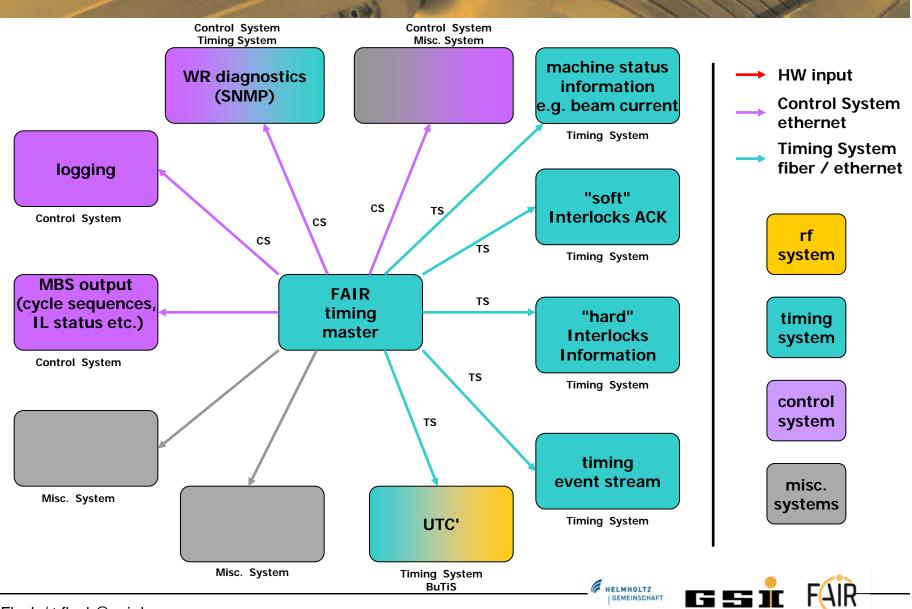

# timing master inputs

# timing master outputs